231

Unit 18 Solutions

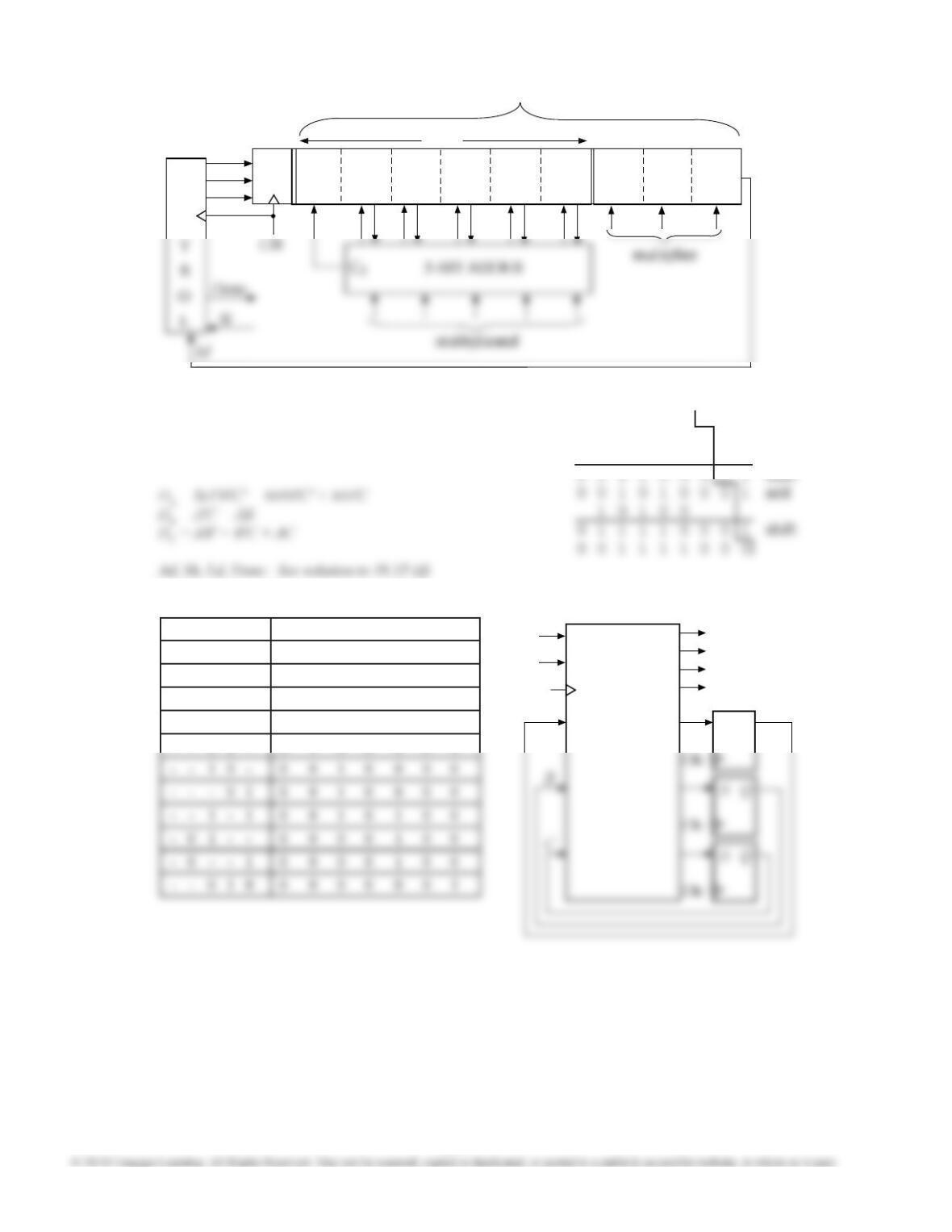

18.12 (a) Inputs and outputs are given in decimal in the table. Inputs 10 through 14 are assumed to never occur.

0 1 2 3 4 5 6 7 8 9 15

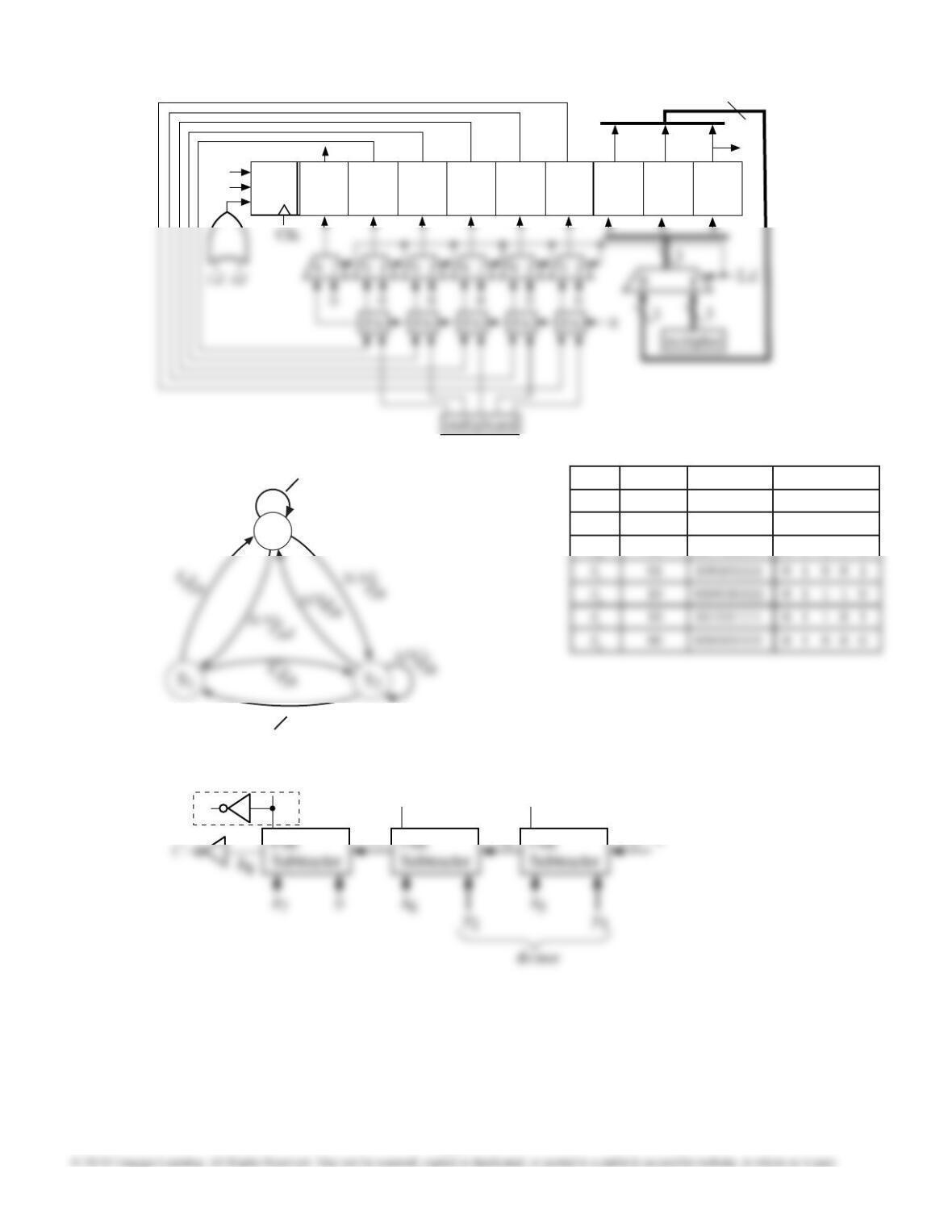

18.13 (a) Inputs and outputs are given in decimal in the table. Inputs 1, 2, 13, 14, and 15 are assumed to never occur.

0 3 4 5 6 7 8 9 10 11 12

A A, 0 A, 3 B, 12 B, 11 B, 10 B, 9 B, 8 B, 7 B, 6 B, 5 B, 4

Use the state assignment Q = 0 for state A and Q = 1 for state B. There are 159 minimum sum-of-product equations

for Q+; one solution is

Q+ = X3'X0 + X3'X2 + X3'X1 + X3X2' + QX2'.

18.12 (b)

Use the state assignment Q = 0 for state A and Q = 1 for state B. The minimum sum-of-product equations for Q+ and

the outputs are

Q+ = X3 + X2 + QX0 or

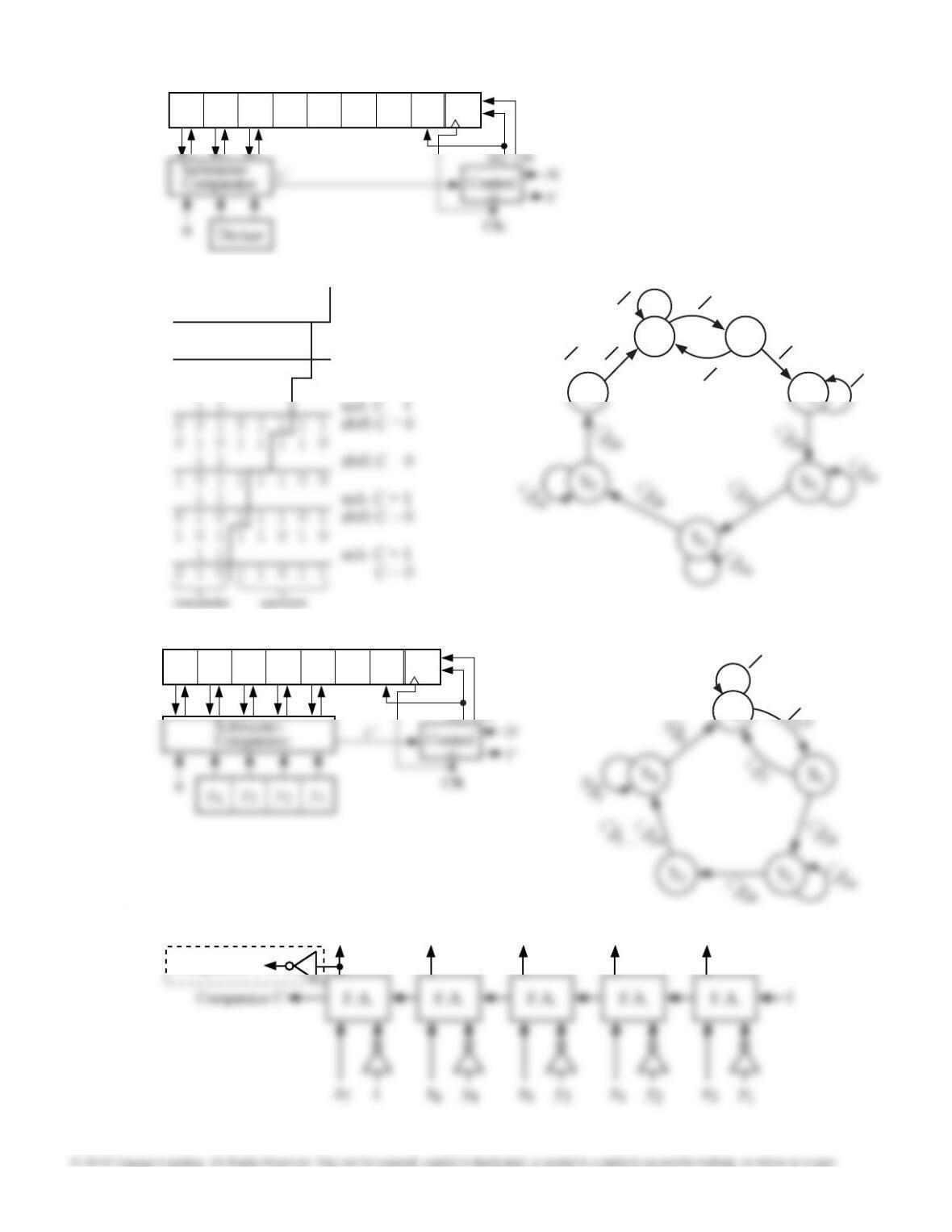

18.13 (b)

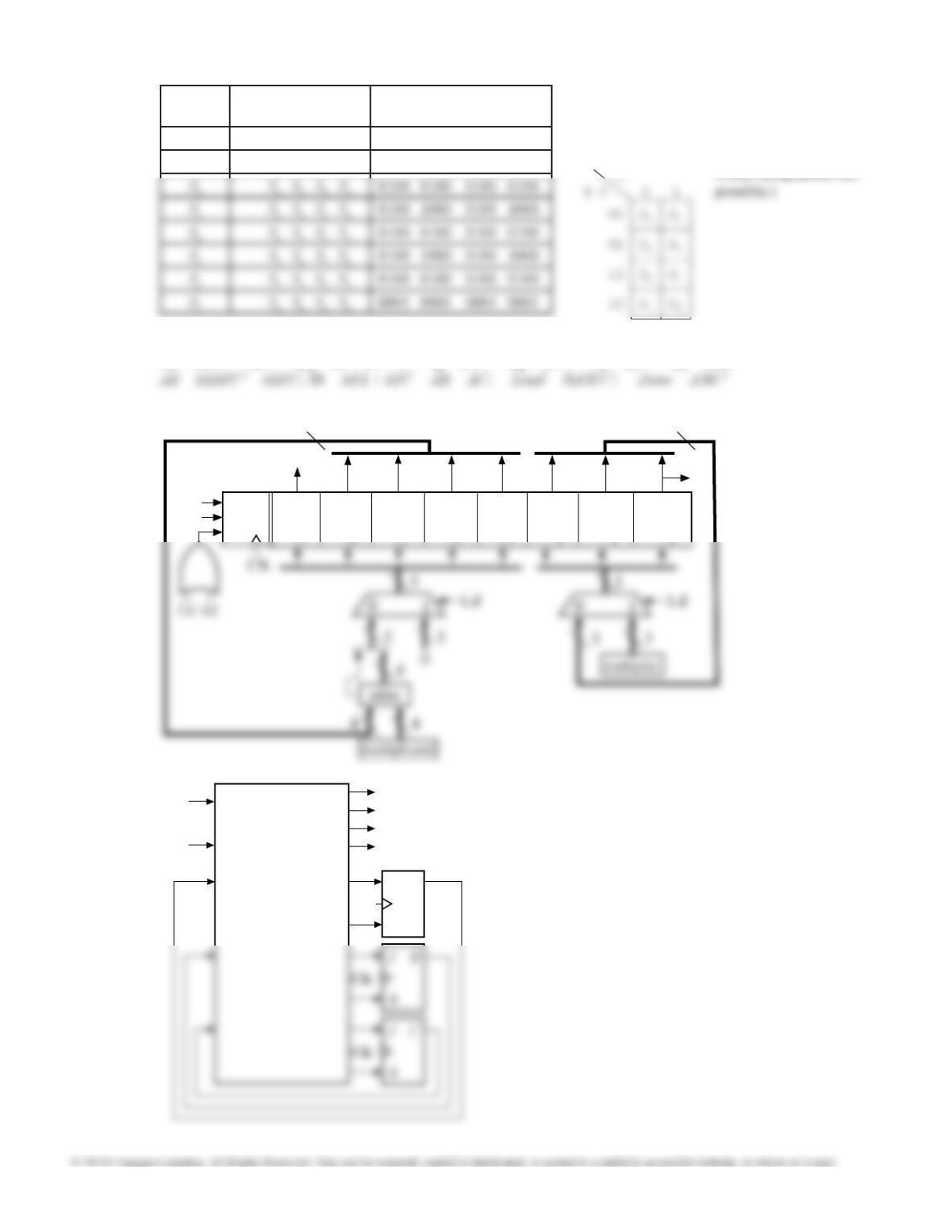

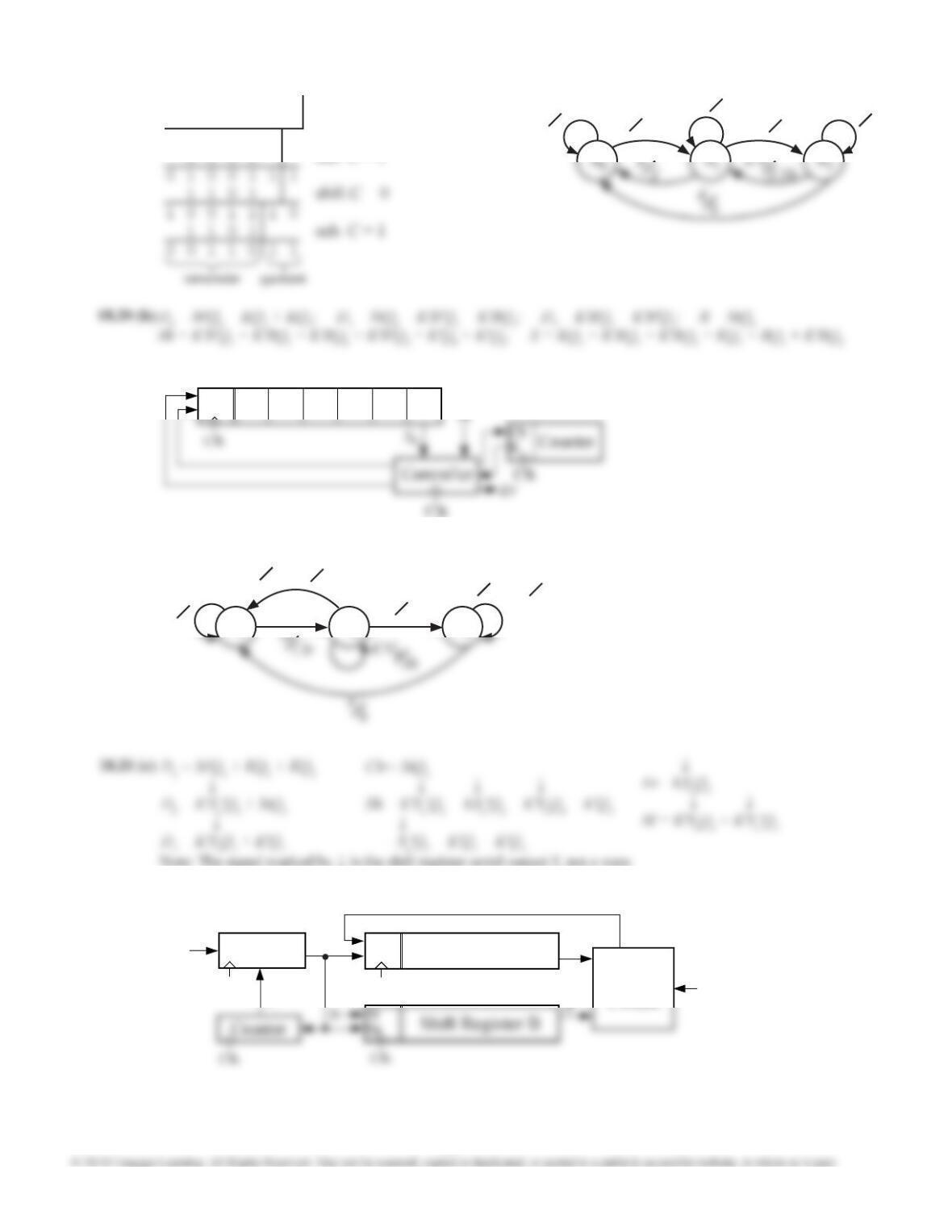

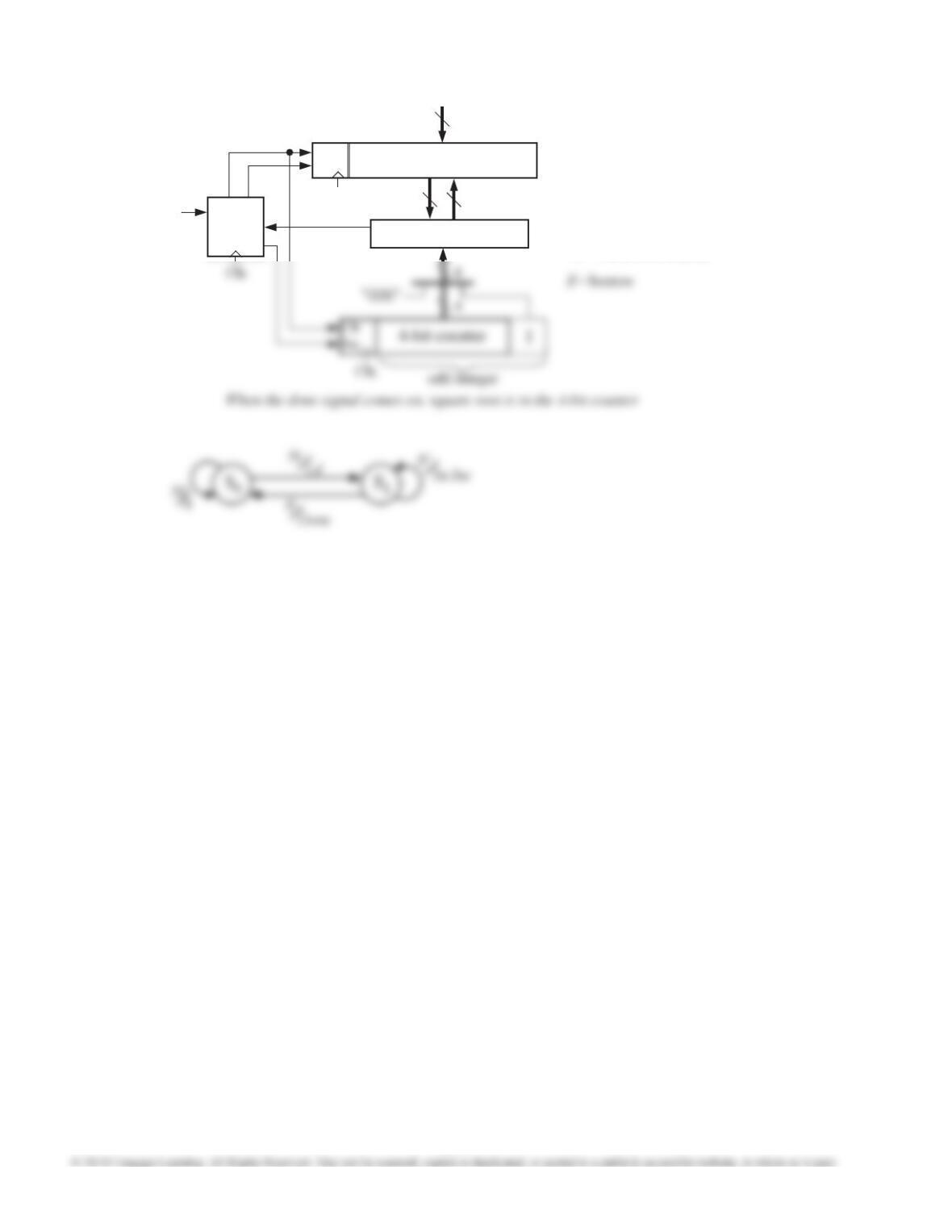

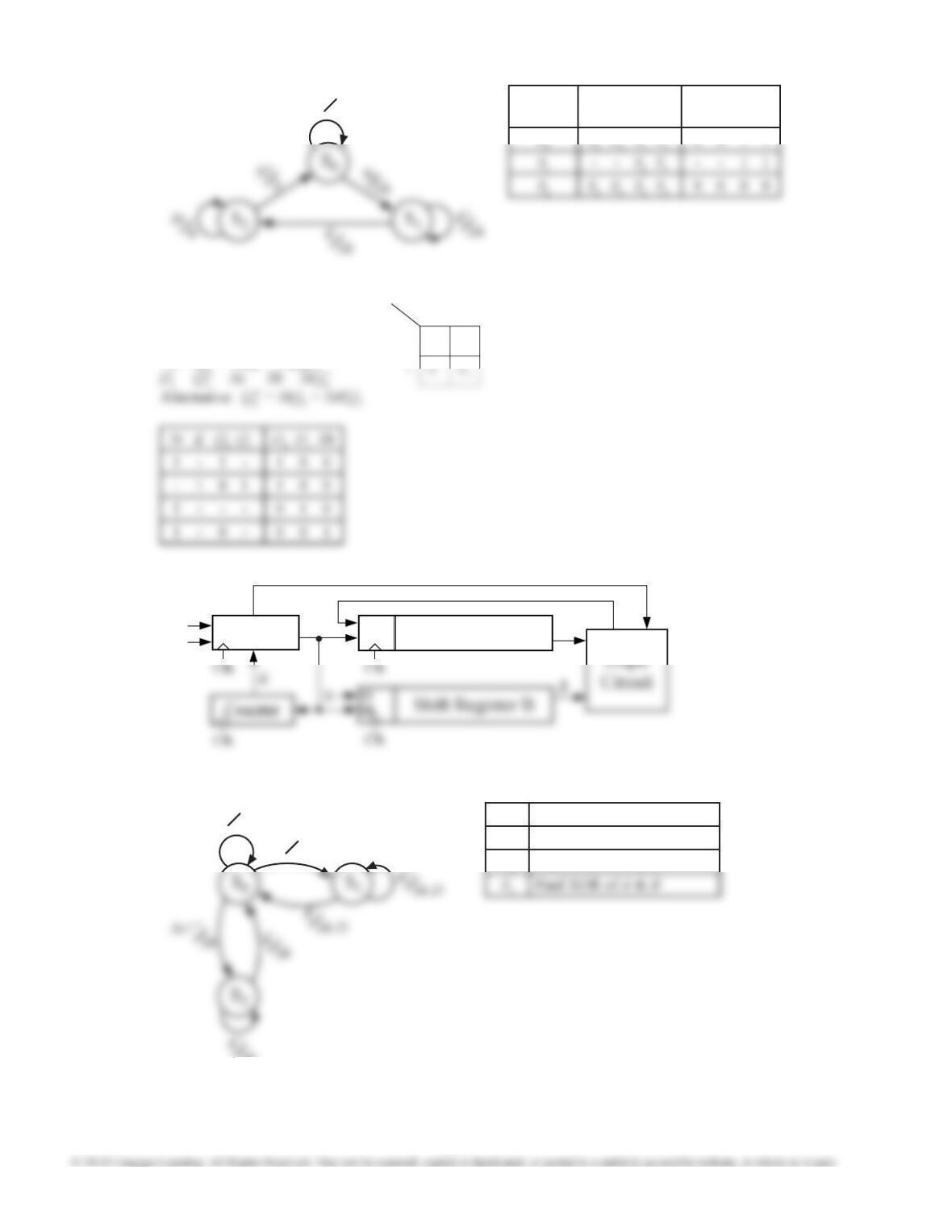

18.14 The ONE ADDER is similar to a serial adder,

except that there is only one input. This means that

the carry will be added to X. Thus, if the carry ip-

op is initially set to 1, 1 will be added to the input.

The signal I can be used to preset the carry ip-op

to 1.

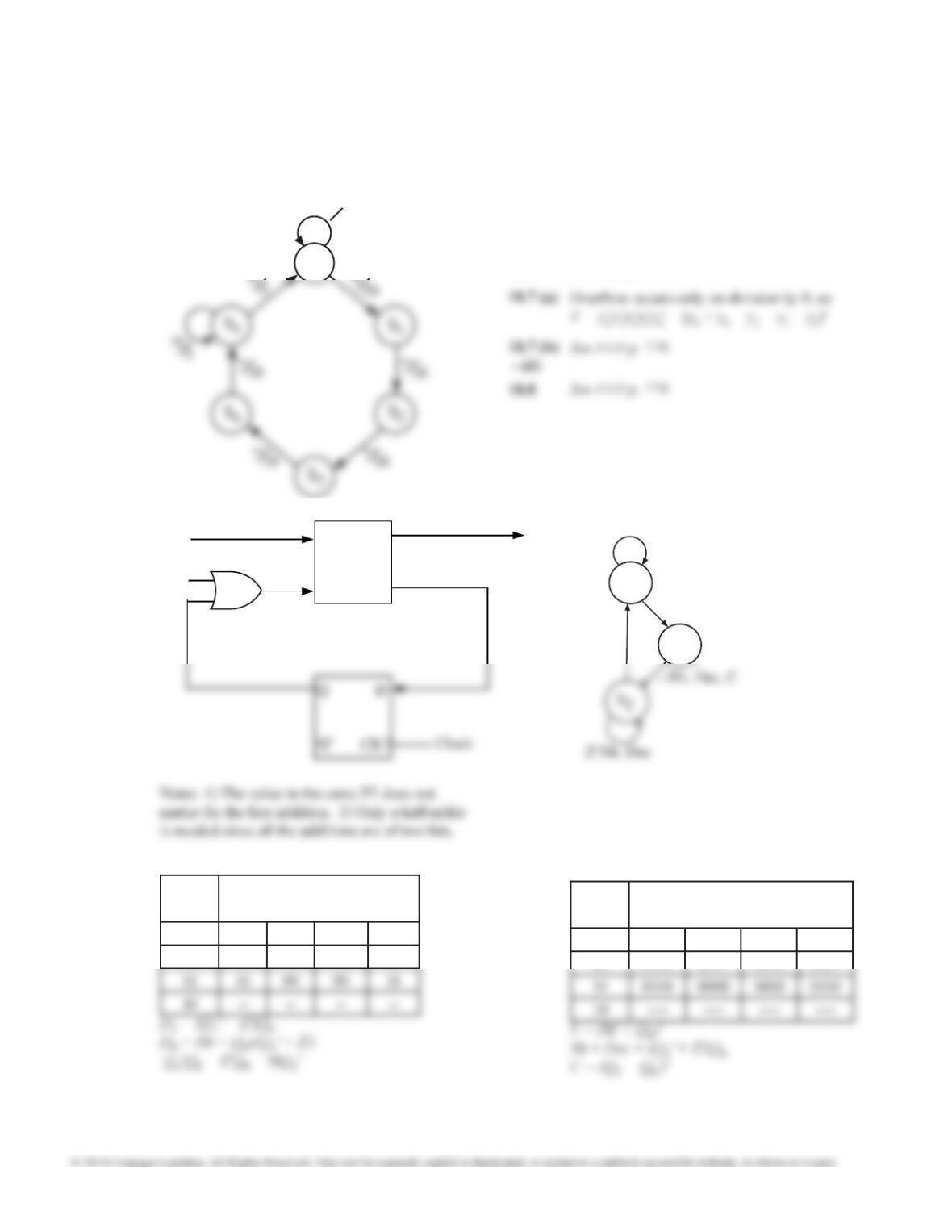

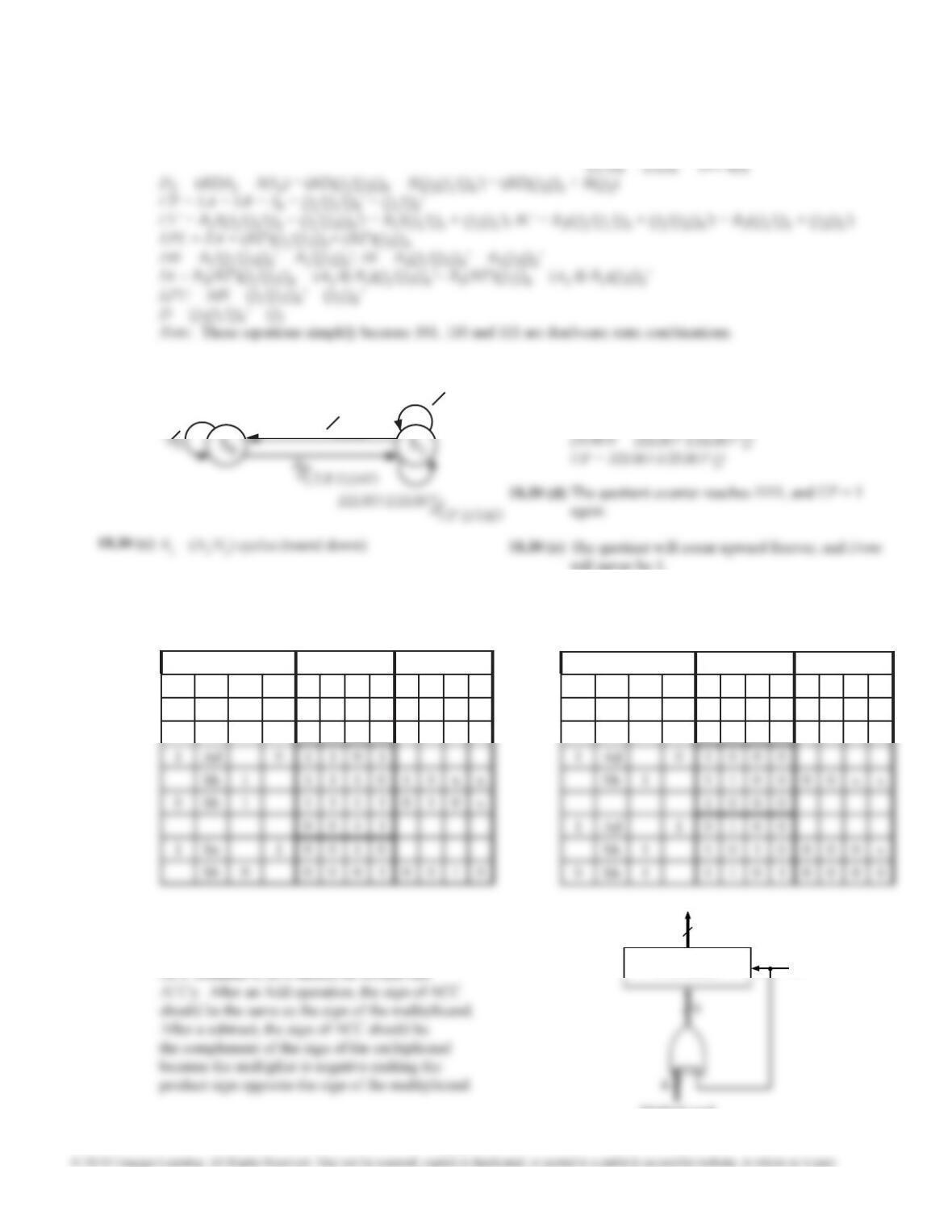

Q

X Sh 0 1

00

01

11

0

0

0

1

0

1

Q

X Sh 0 1

00

01

11

0

0

1

0

1

0