50)/300 = 83.3%. Thus, given the same num-

ber of defects per wafer, the wafer with smaller

chips (i.e., more chips per wafer) will have a

13.50 A chlorine-based polysilicon etch process dis-

resist and exposed oxide will be consumed in

etching 350 nm of polysilicon? What should

the polysilicon:oxide selectivity be in order to

remove only 4 nm of exposed oxide?

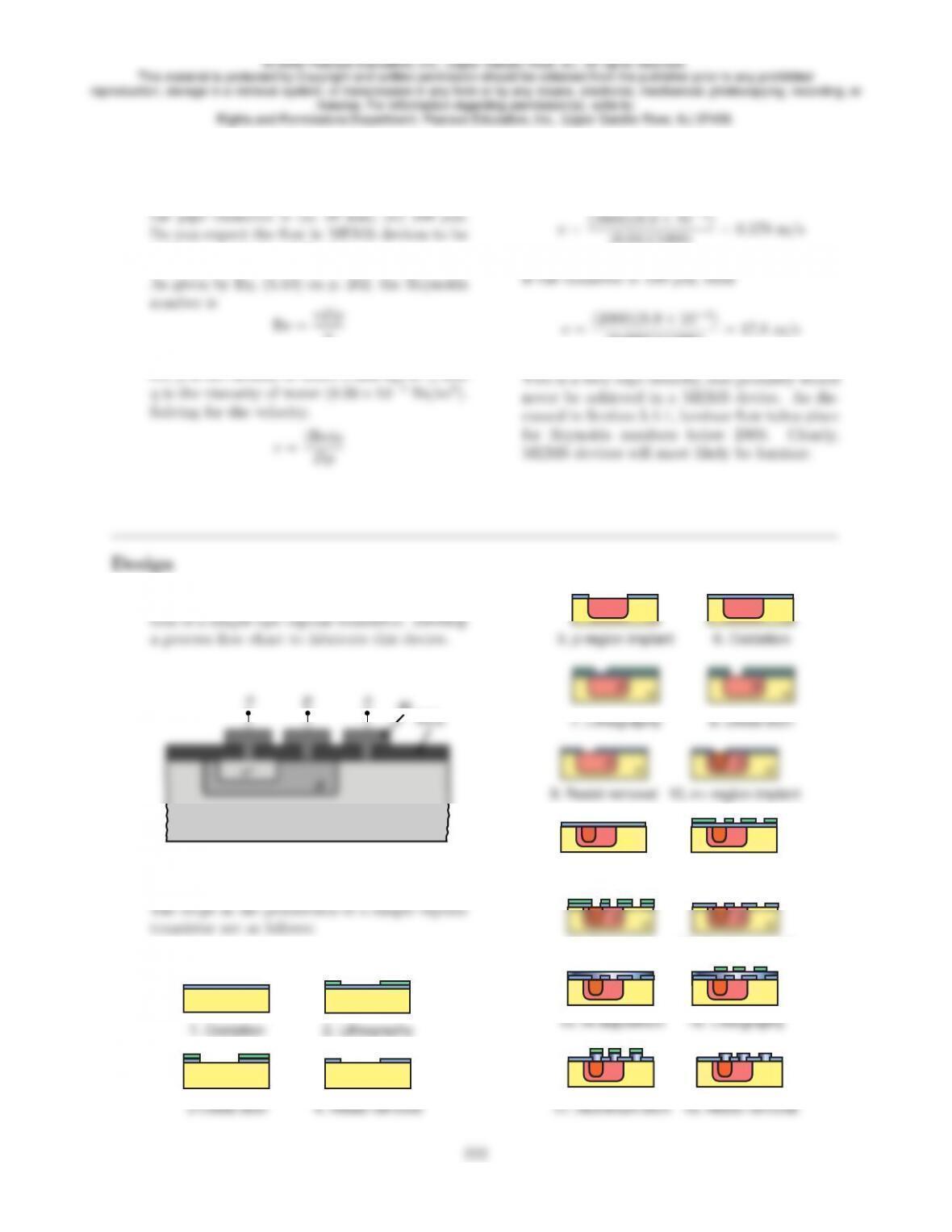

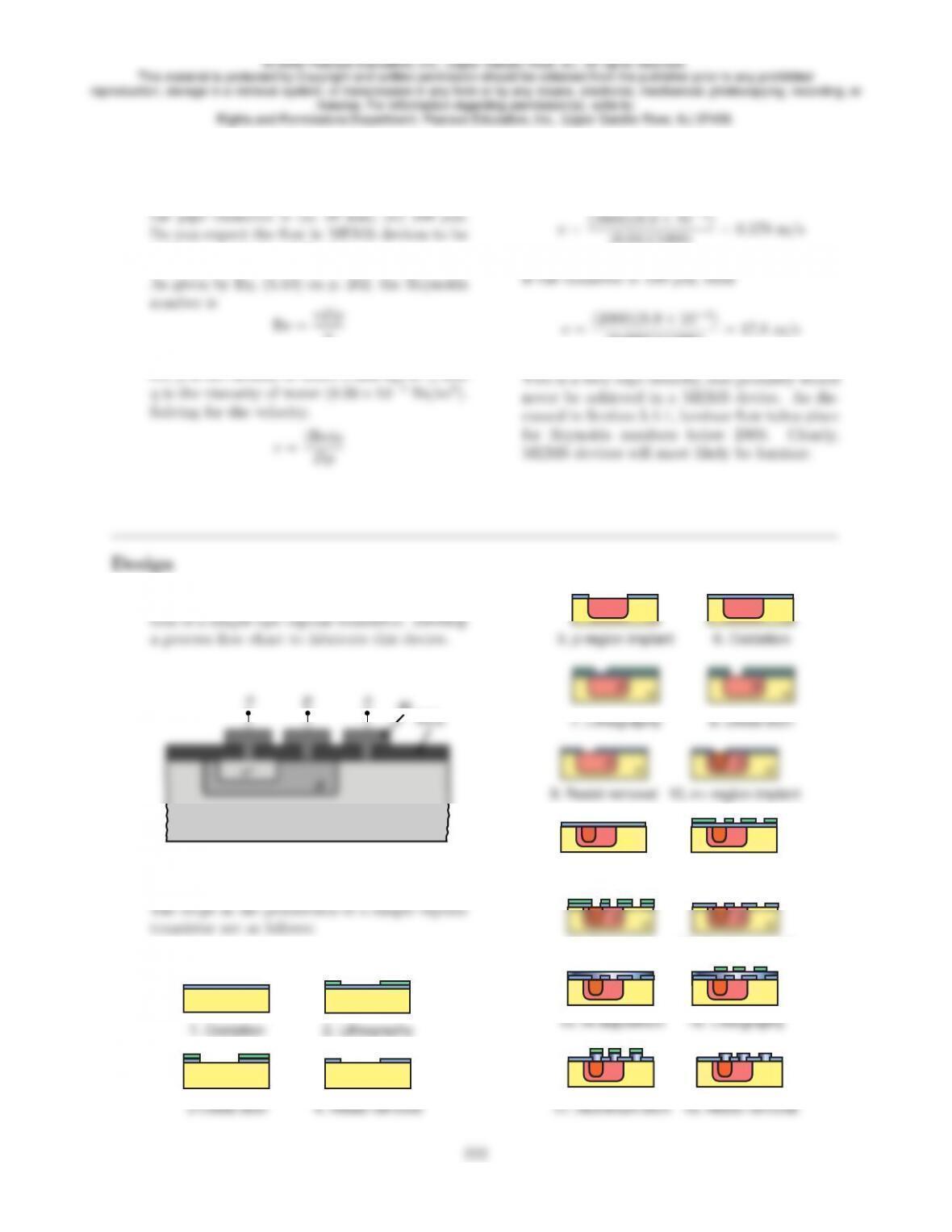

13.51 During a processing sequence, four silicon-

dioxide layers are grown by oxidation: 400 nm,

150 nm, 40 nm, and 15 nm. How much of the

silicon substrate is consumed?

13.6, the ratio of oxide to the amount of silicon

13.52 A certain design rule calls for metal lines to be

no less than 2 µm wide. If a 1 µm-thick metal

layer is to be wet etched, what is the minimum

photoresist width allowed? (Assume that the

wet etch is perfectly isotropic.) What would be

the minimum photoresist width if a perfectly

anisotropic dry-etch process were used?

A perfectly isotropic wet-etch process will etch

equally in the vertical and horizontal directions.

Therefore, the wet-etch process requires a min-

imum photoresist width of 2 µm, plus 1 µm per

side, to allow for the undercutting, hence a to-

2µ.

13.53 Using Fig. 13.18, obtain mathematical expres-

sions for the etch rate as a function of temper-

Direc- 1/T Etch rate ln(Etch

3.3 4 1.386

h100i2.55 70 4.248

3.3 2 0.6931

h111i2.55 2 0.6931

3.3 0.015 -4.200

ln(y) vs. 1/T curve, and bis the y-intercept.

From the data in the table above, we can ob-

tain the following

h111i-6.524 17.33

in the h100idirection:

y=1.236 ×107e−4.74/T

in the h111idirection:

y=3.3×107e−6.524/T

13.54 If a square mask of side length 100 µm is

placed on a {100}plane and oriented with a

side in the h110idirection, how long will it

take to etch a hole 4 µm deep at 80◦C using

ethylene-diamine/pyrocatechol? Sketch the re-

© 2008 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved.

This material is protected by Copyright and written permission should be obtained from the publisher prior to any prohibited

reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or

likewise. For information regarding permission(s), write to:

Rights and Permissions Department, Pearson Education, Inc., Upper Saddle River, NJ 07458.