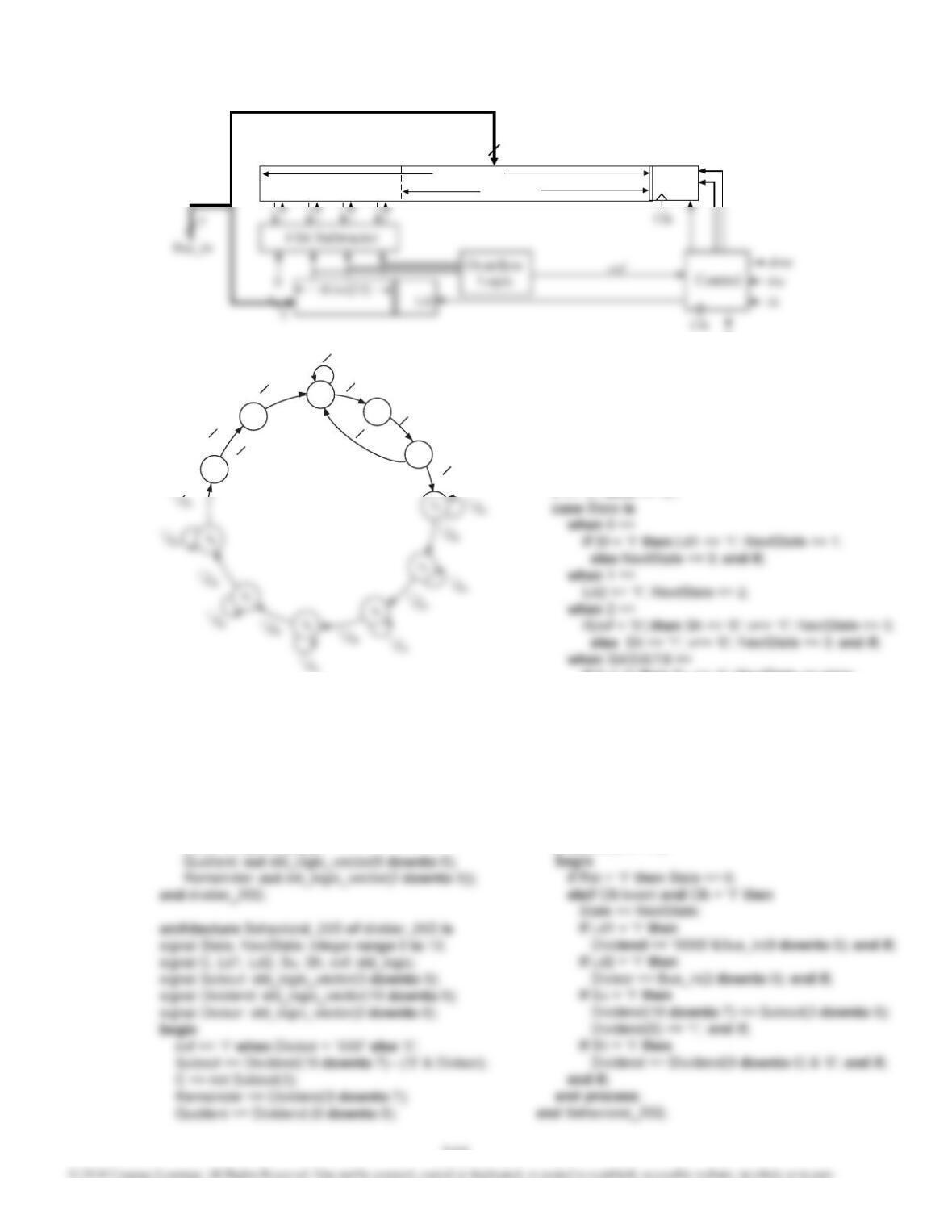

341

Unit 20 Design Solutions

20.P

(cont.)

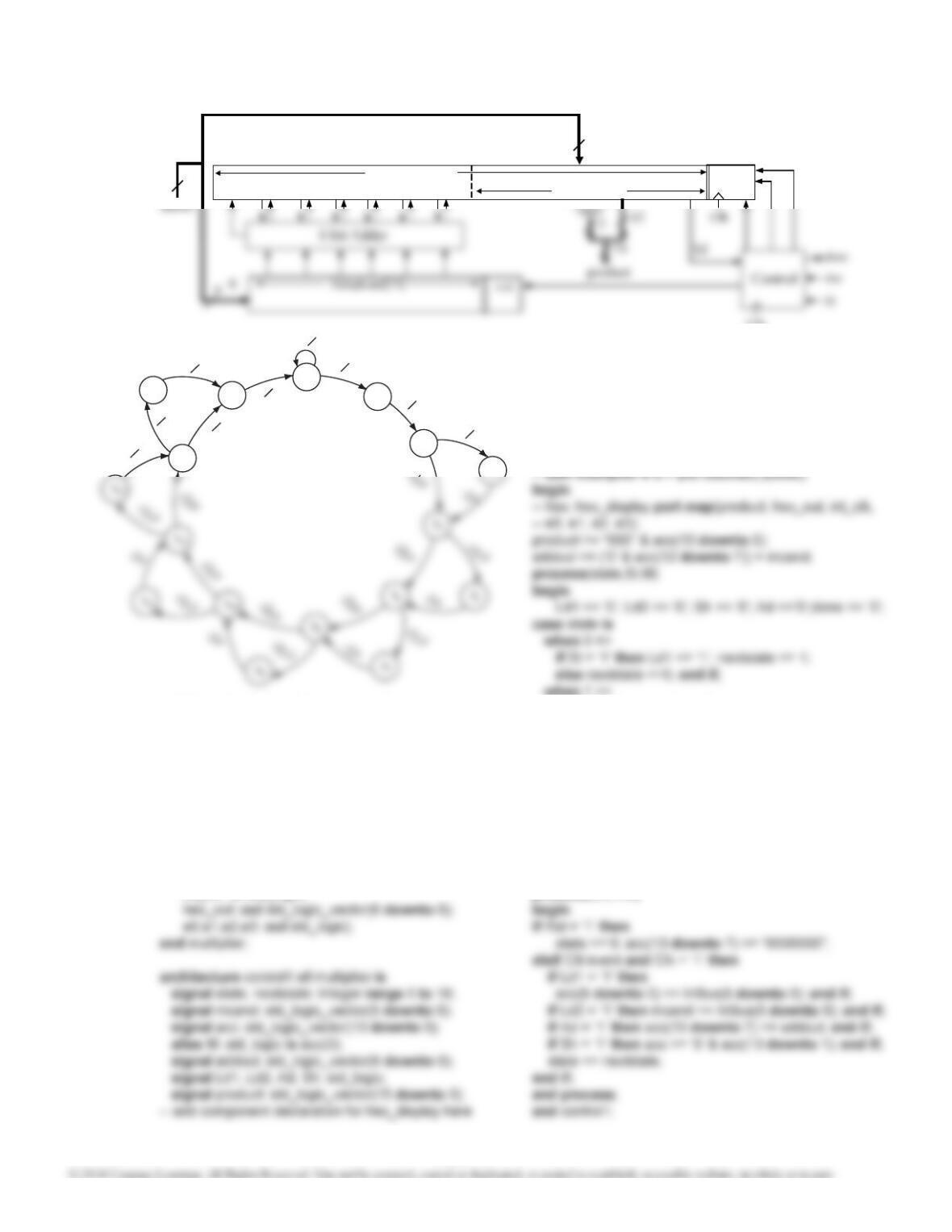

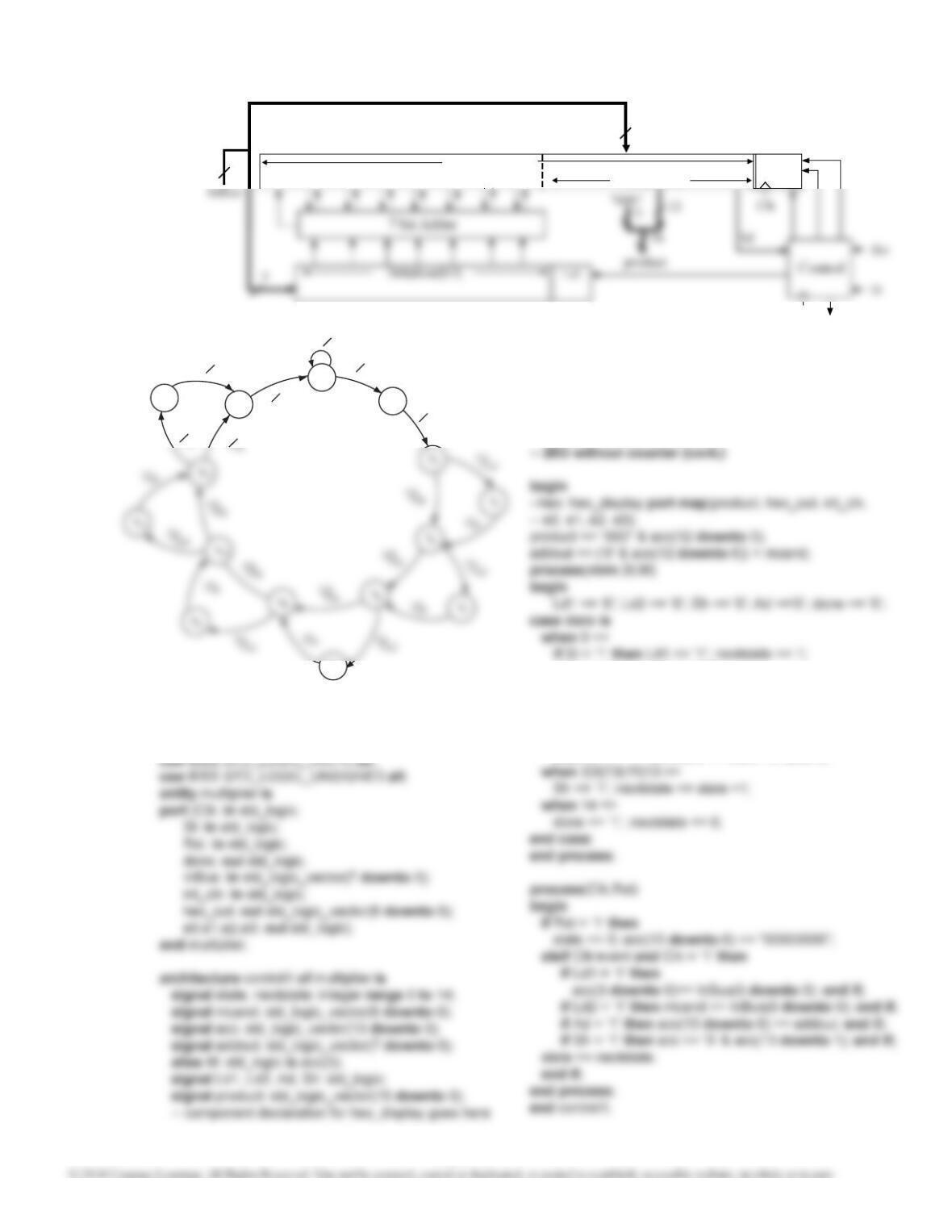

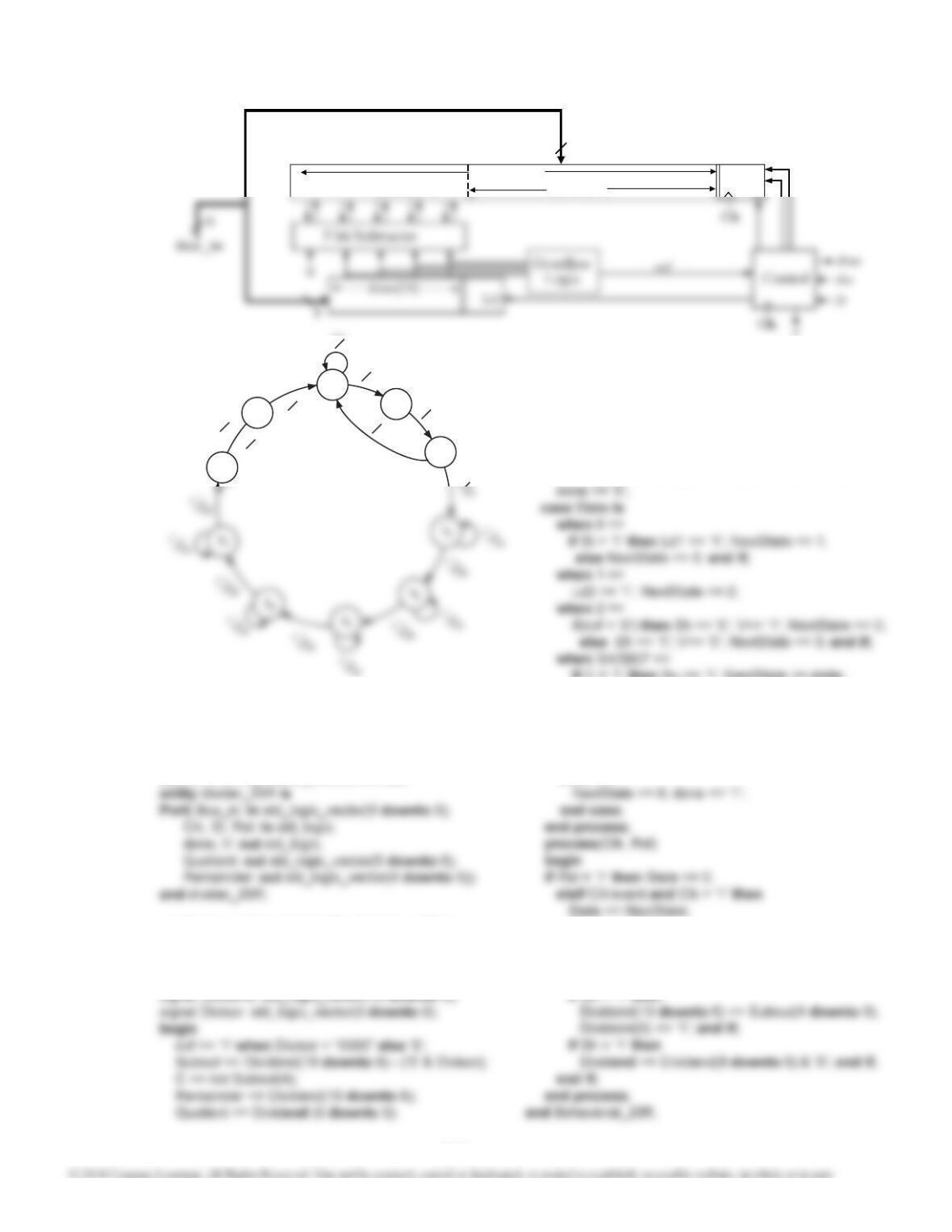

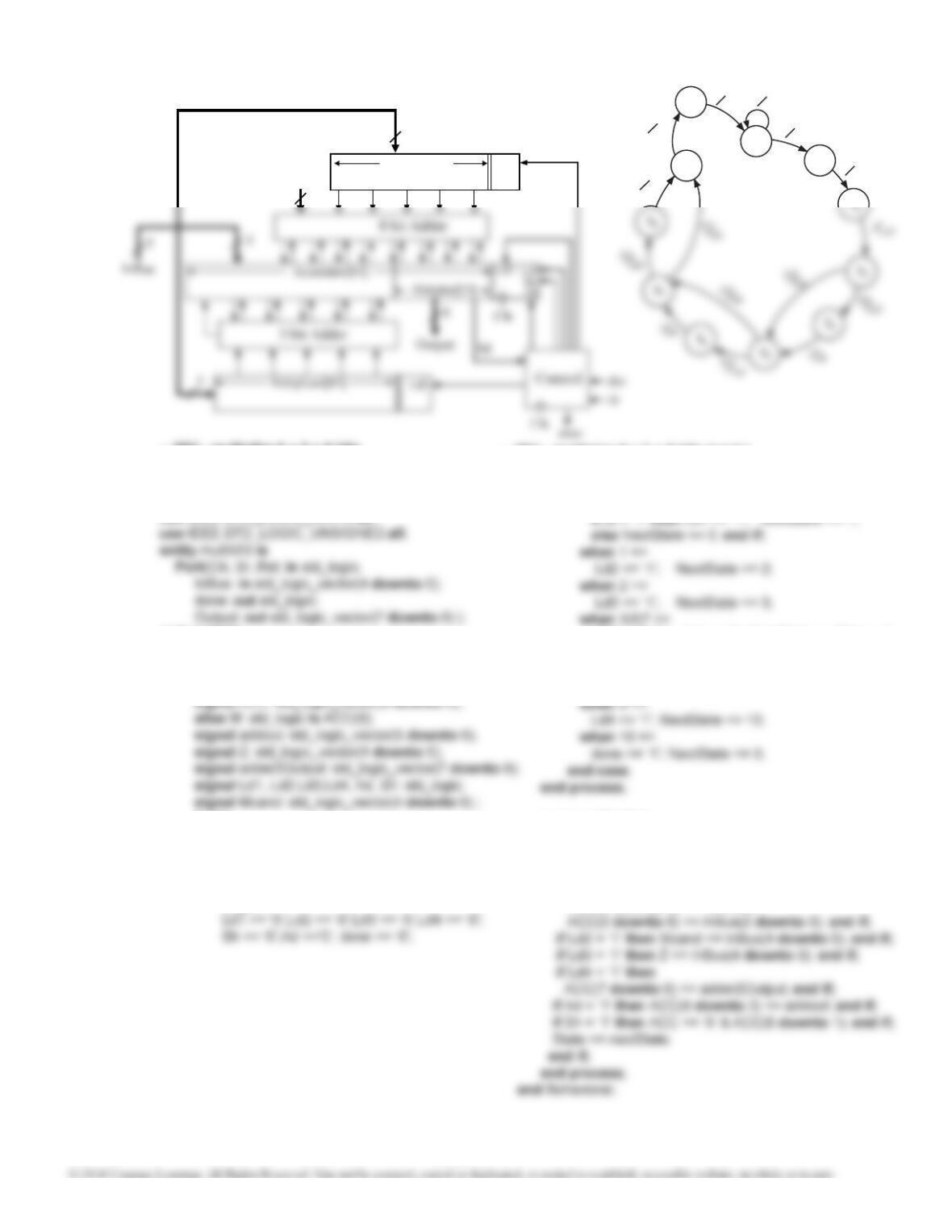

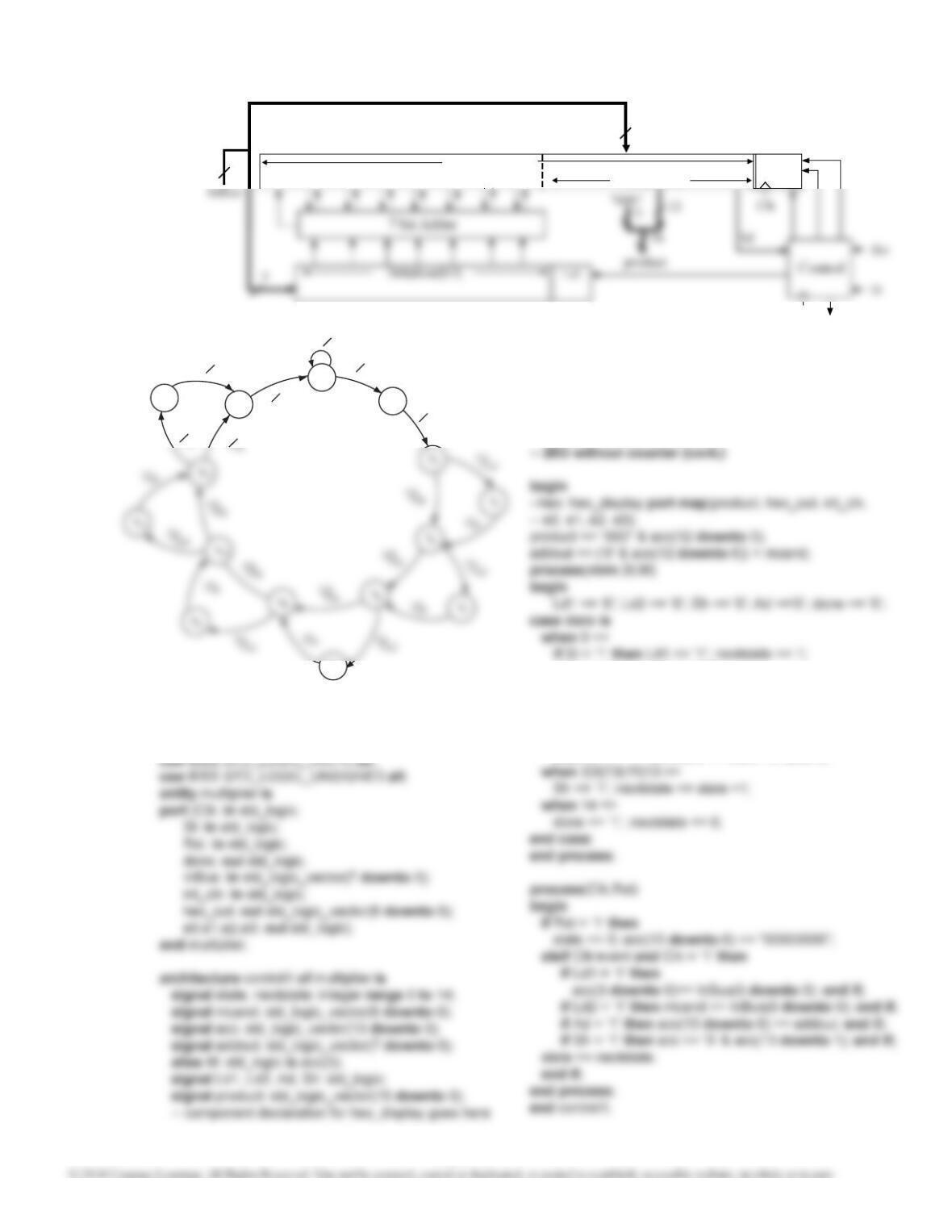

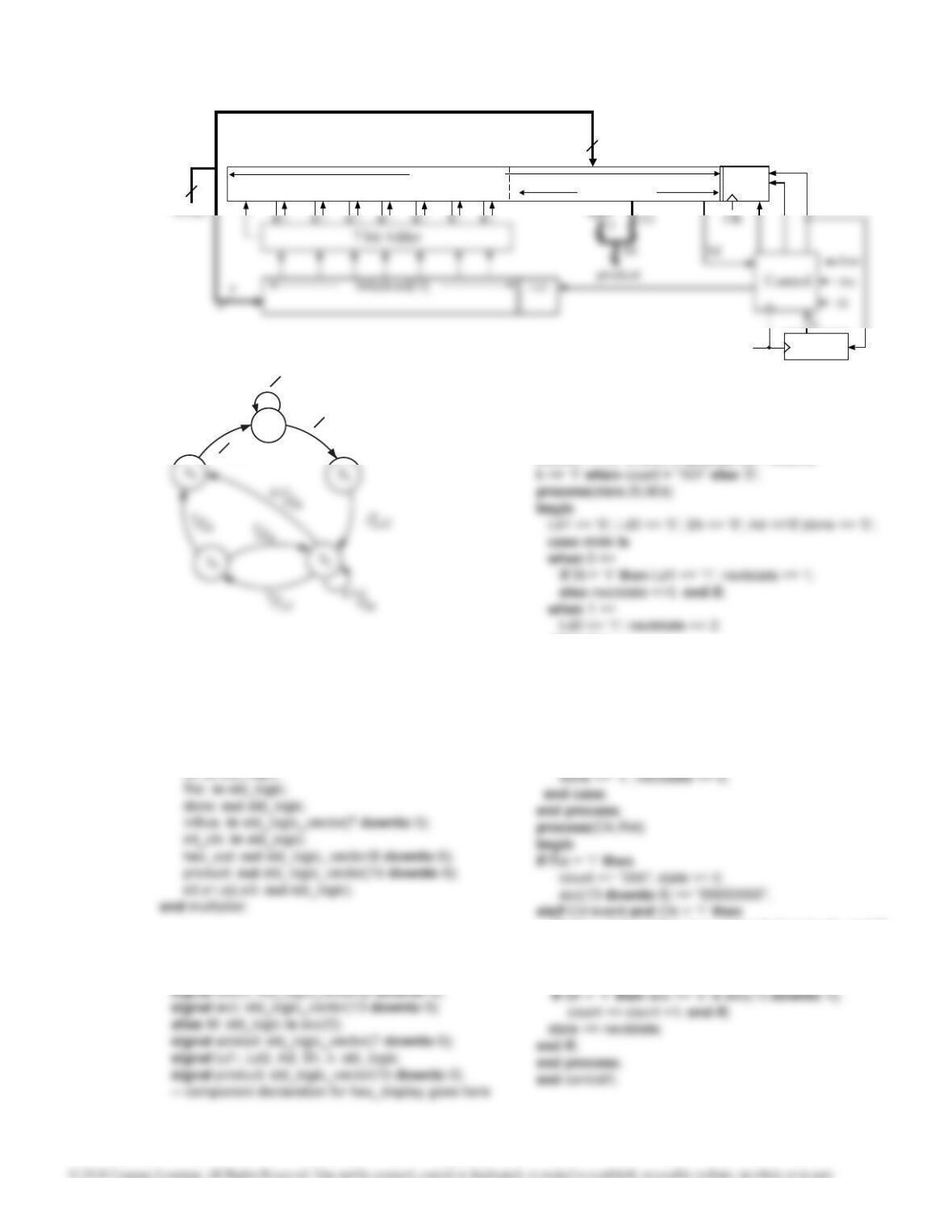

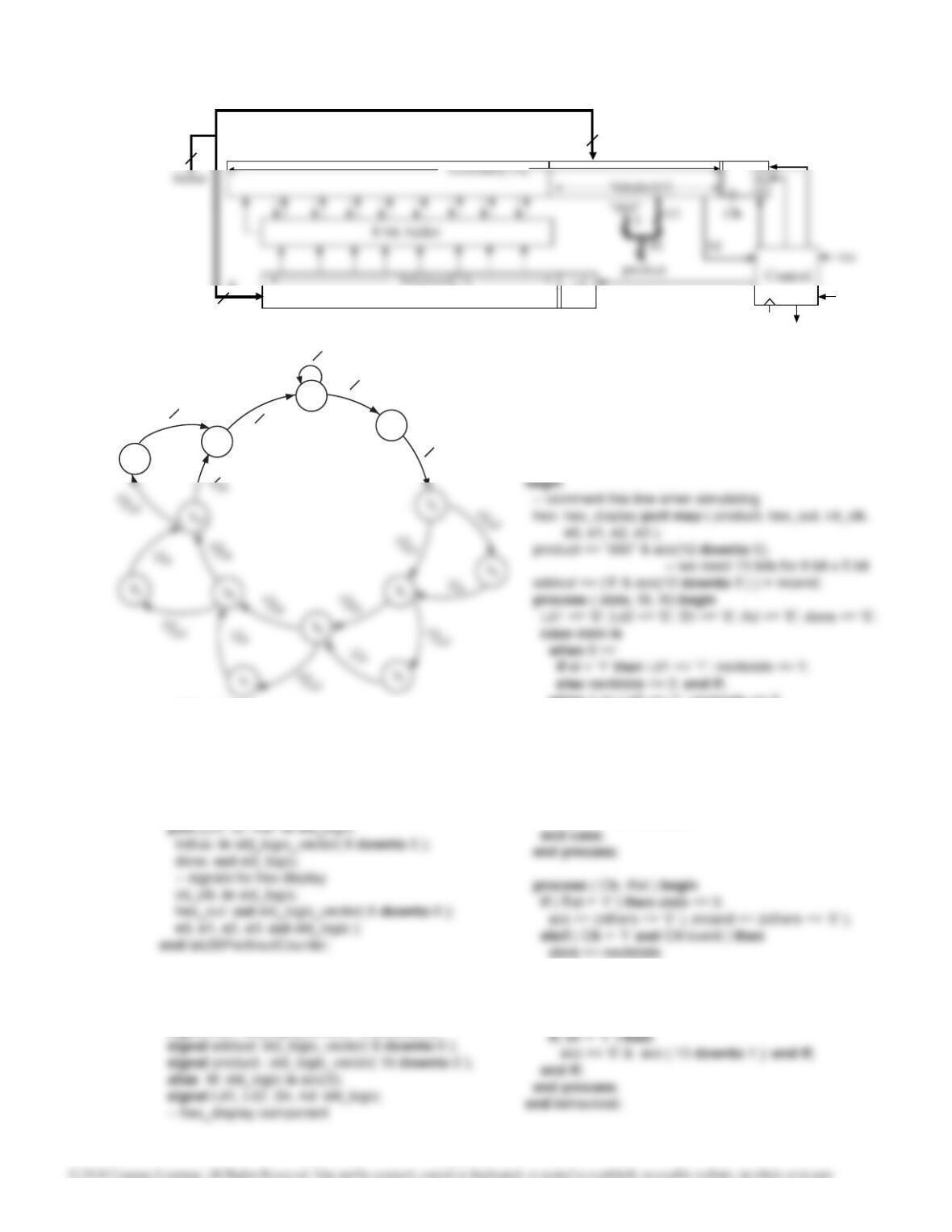

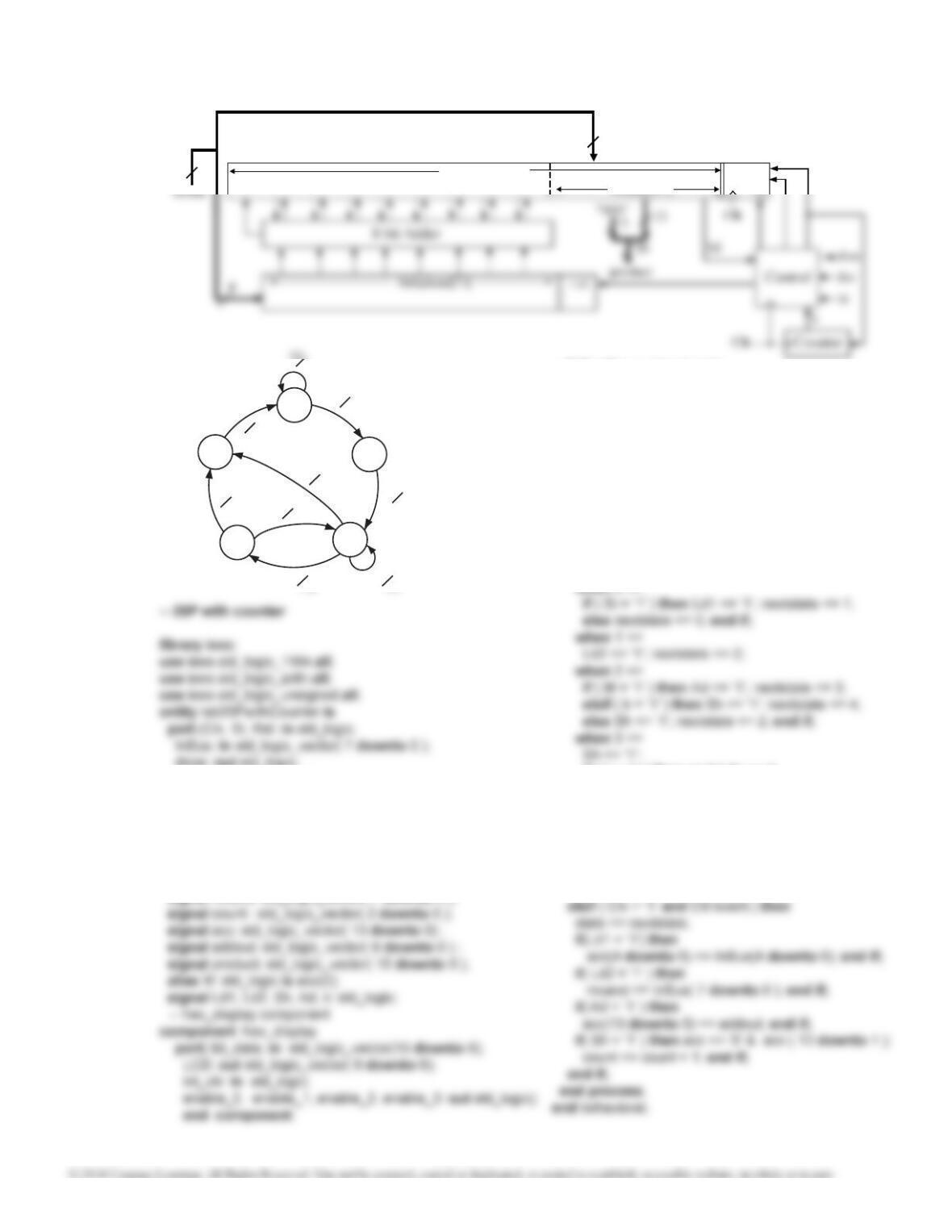

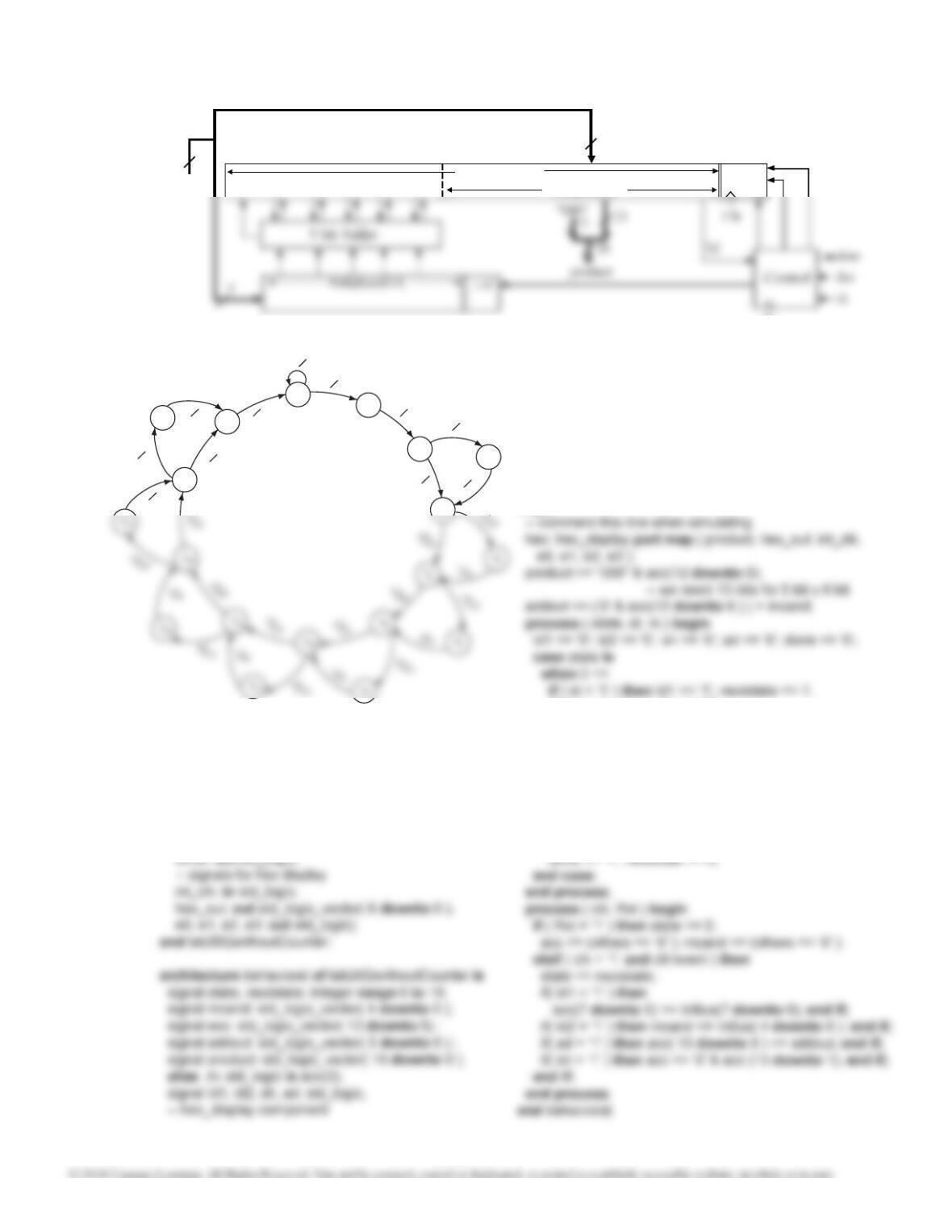

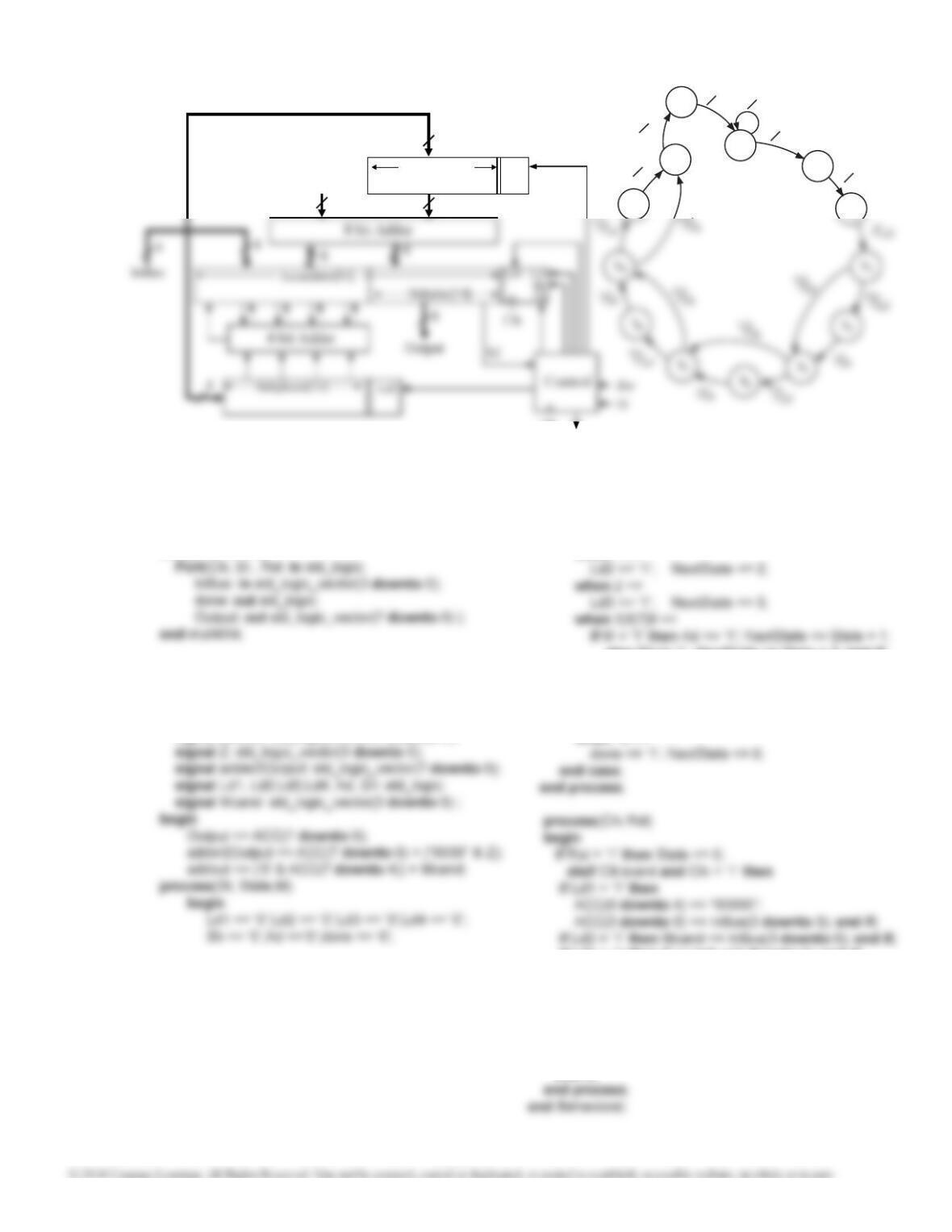

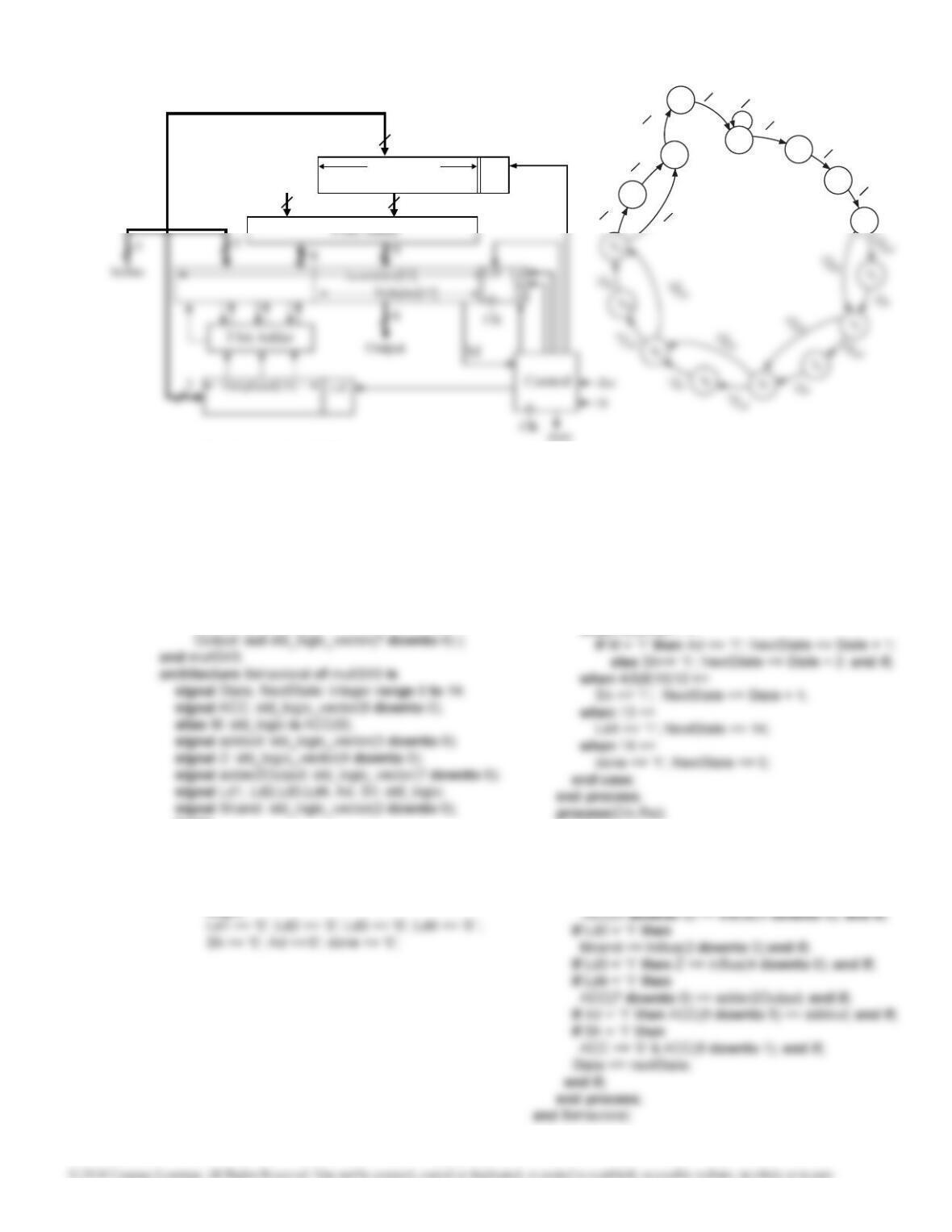

20P with counter

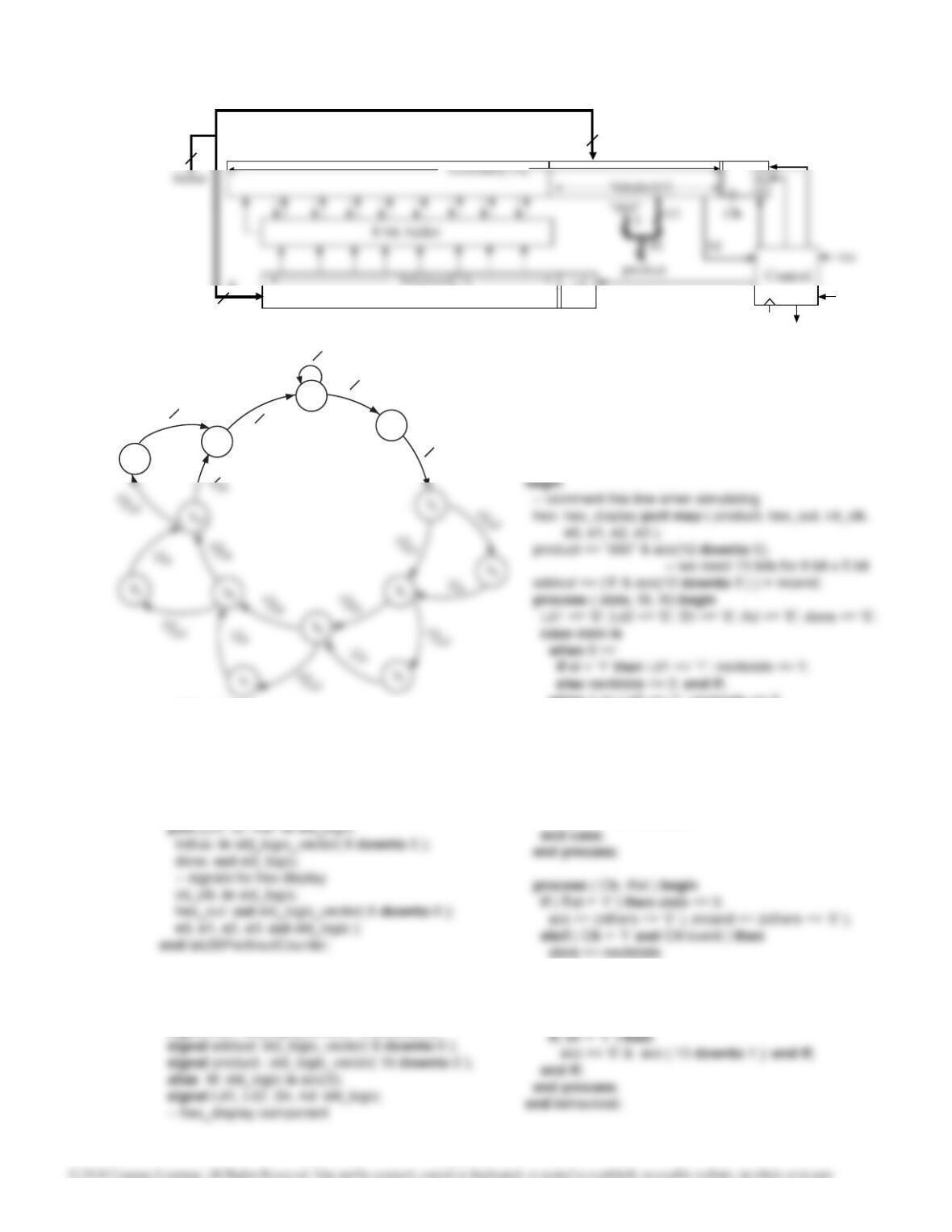

Accumulator[13:0]

Multiplier[4:0]

8Sh

Ld1

5

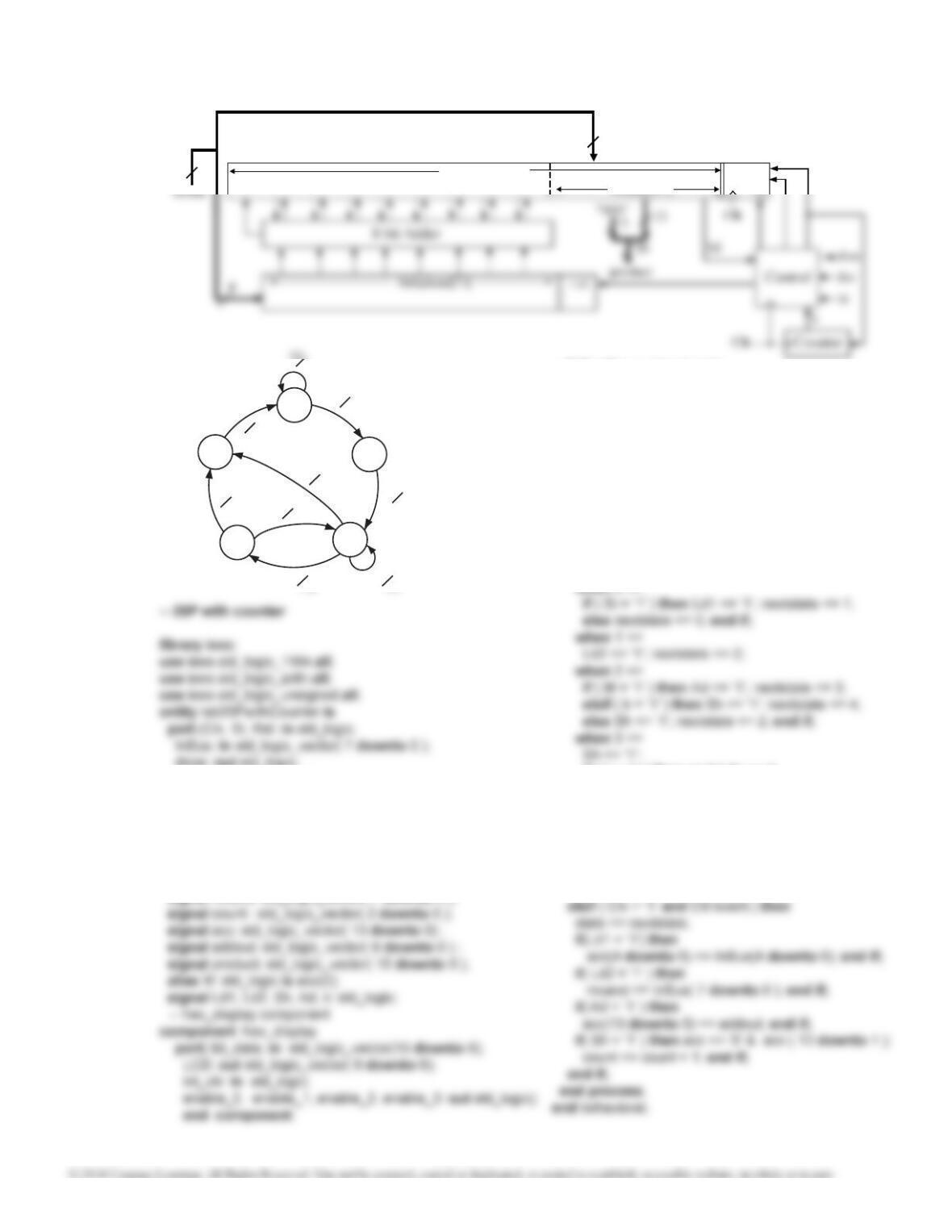

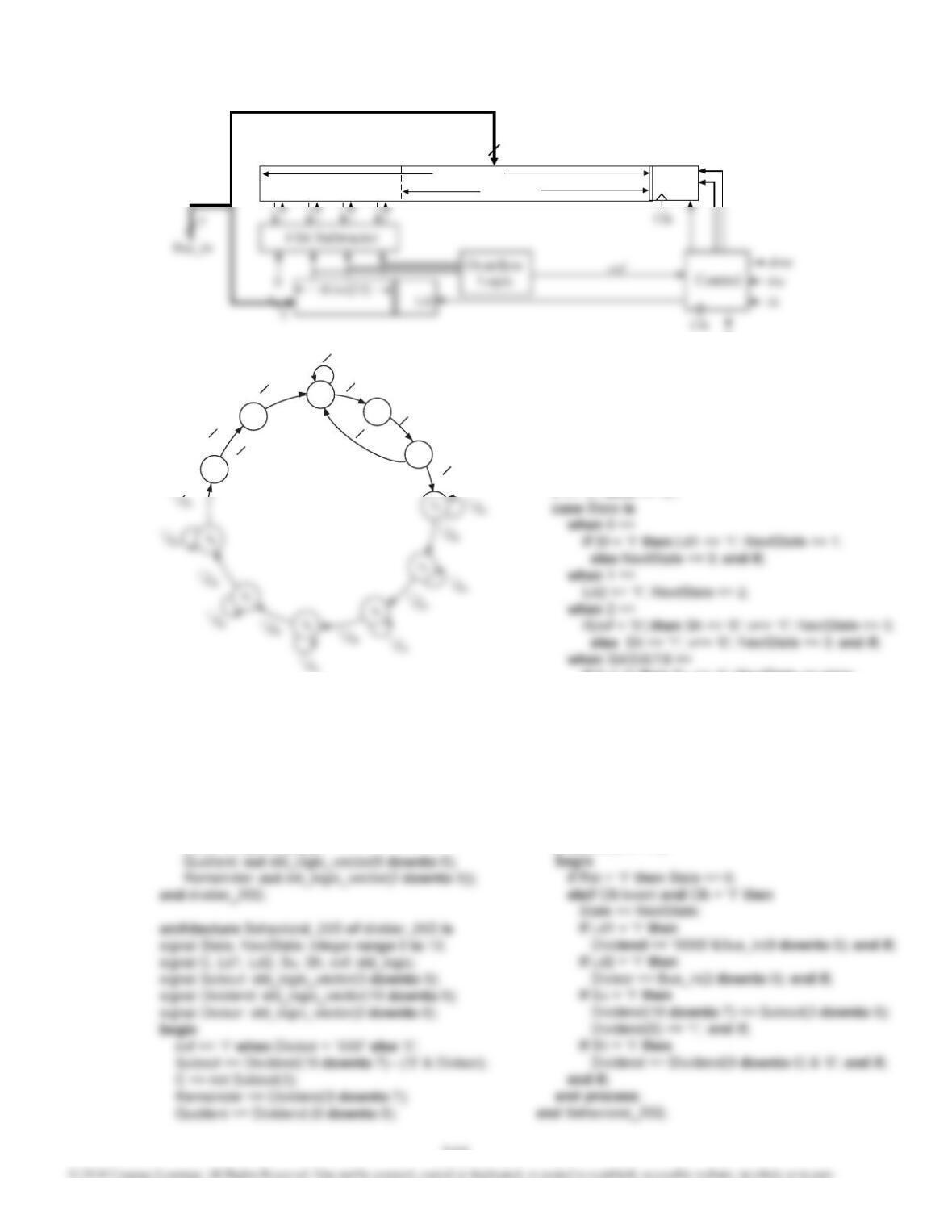

With Counter:

St'0

S1

S0

S3

S4

St Ld1

-Ld2

MAd

k Sh k'Sh

-done

k'M'

Sh

S2

kM'

Sh

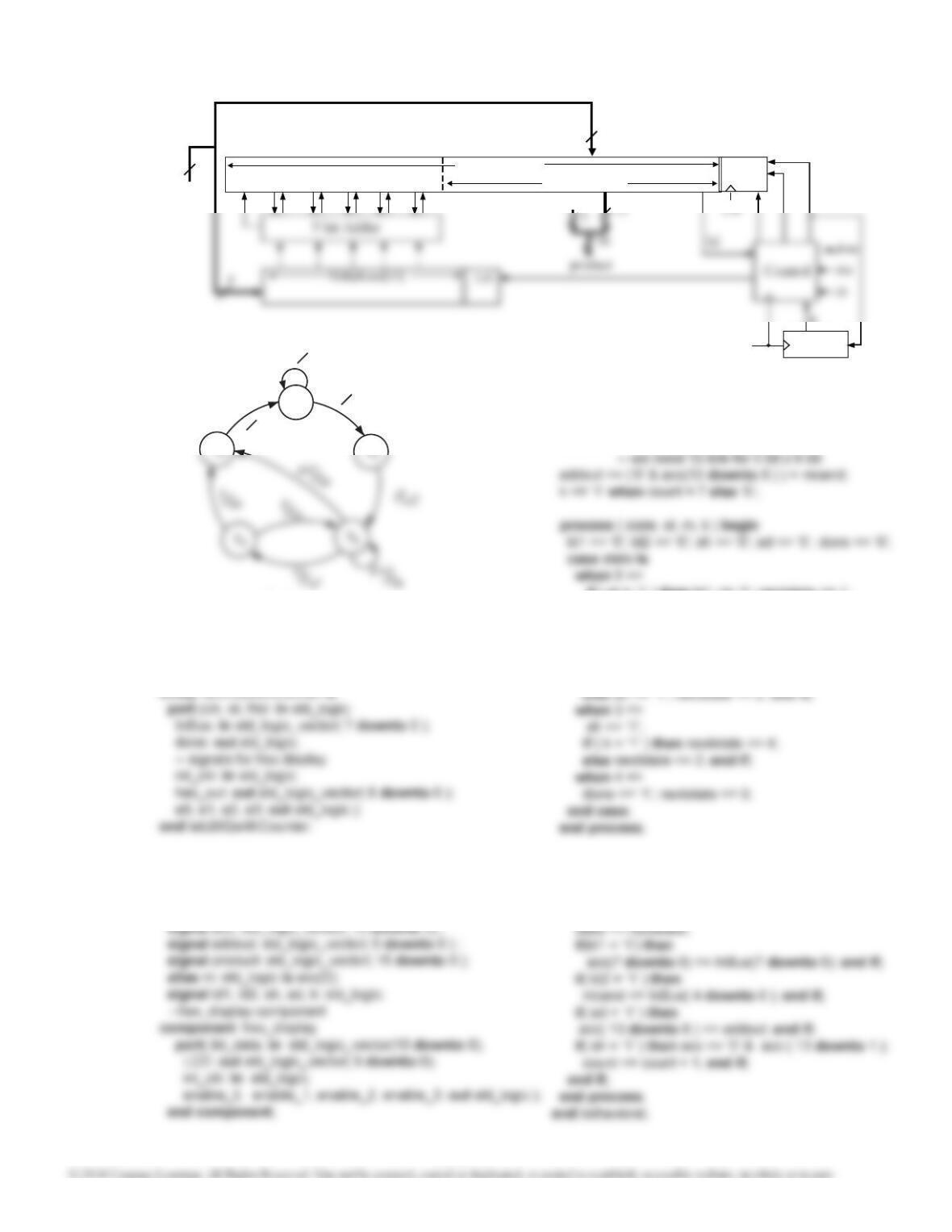

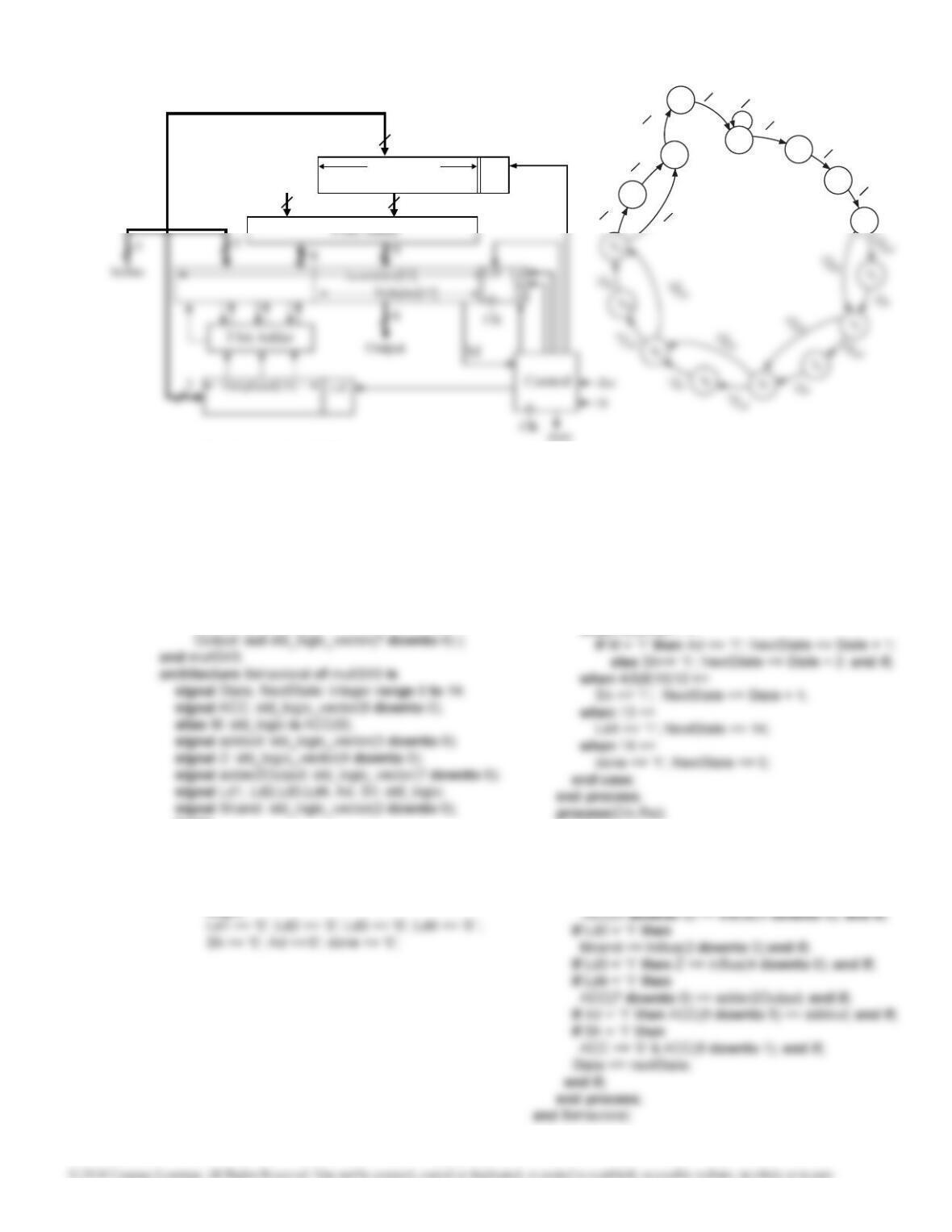

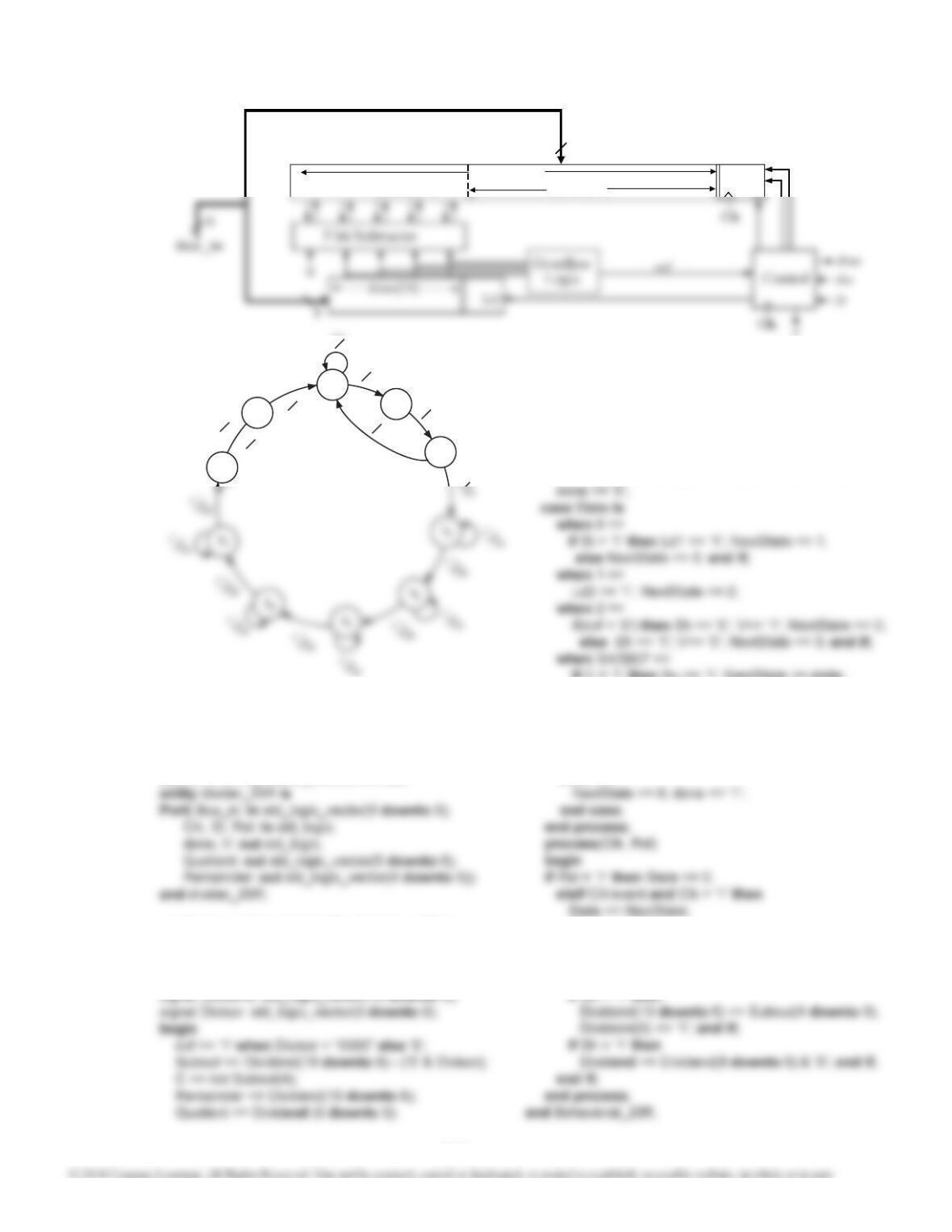

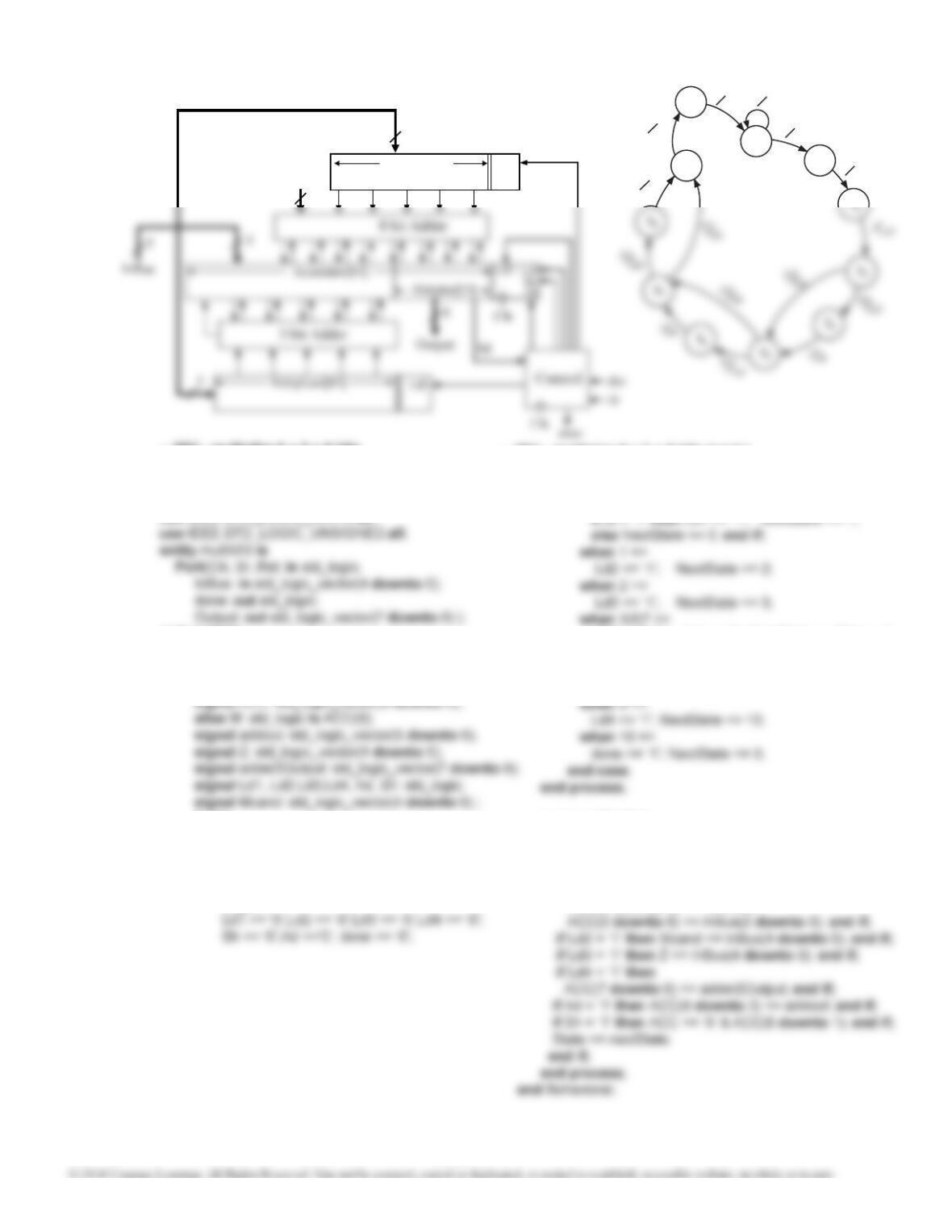

done: out std_logic;

-- signals for hex display

int_clk: in std_logic;

hex_out: out std_logic_vector( 6 downto 0 );

e0, e1, e2, e3: out std_logic );

end lab20PwithCounter;

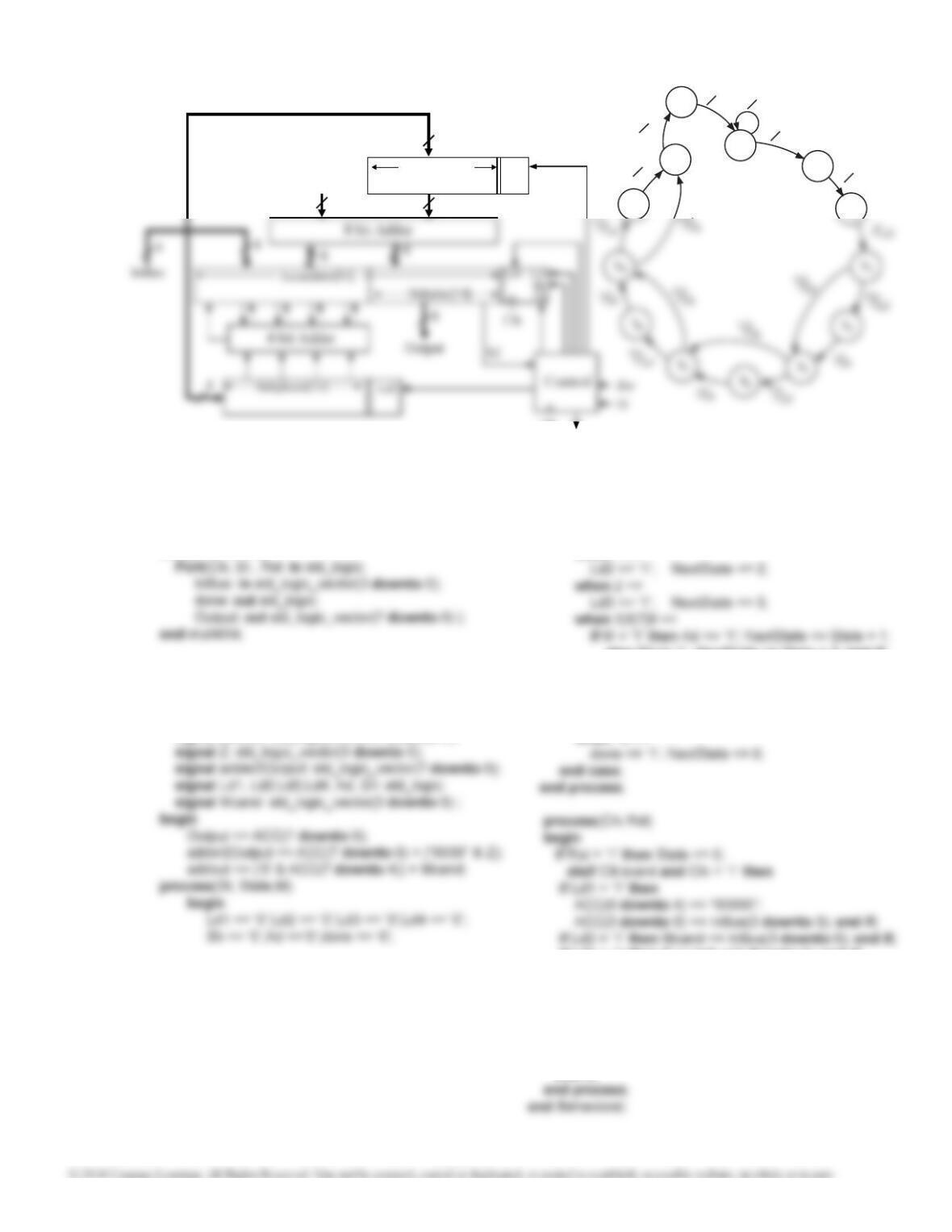

architecture behavioral of lab20PwithCounter is

signal state, nextstate: integer range 0 to 4;

signal mcand: std_logic_vector( 7 downto 0 );

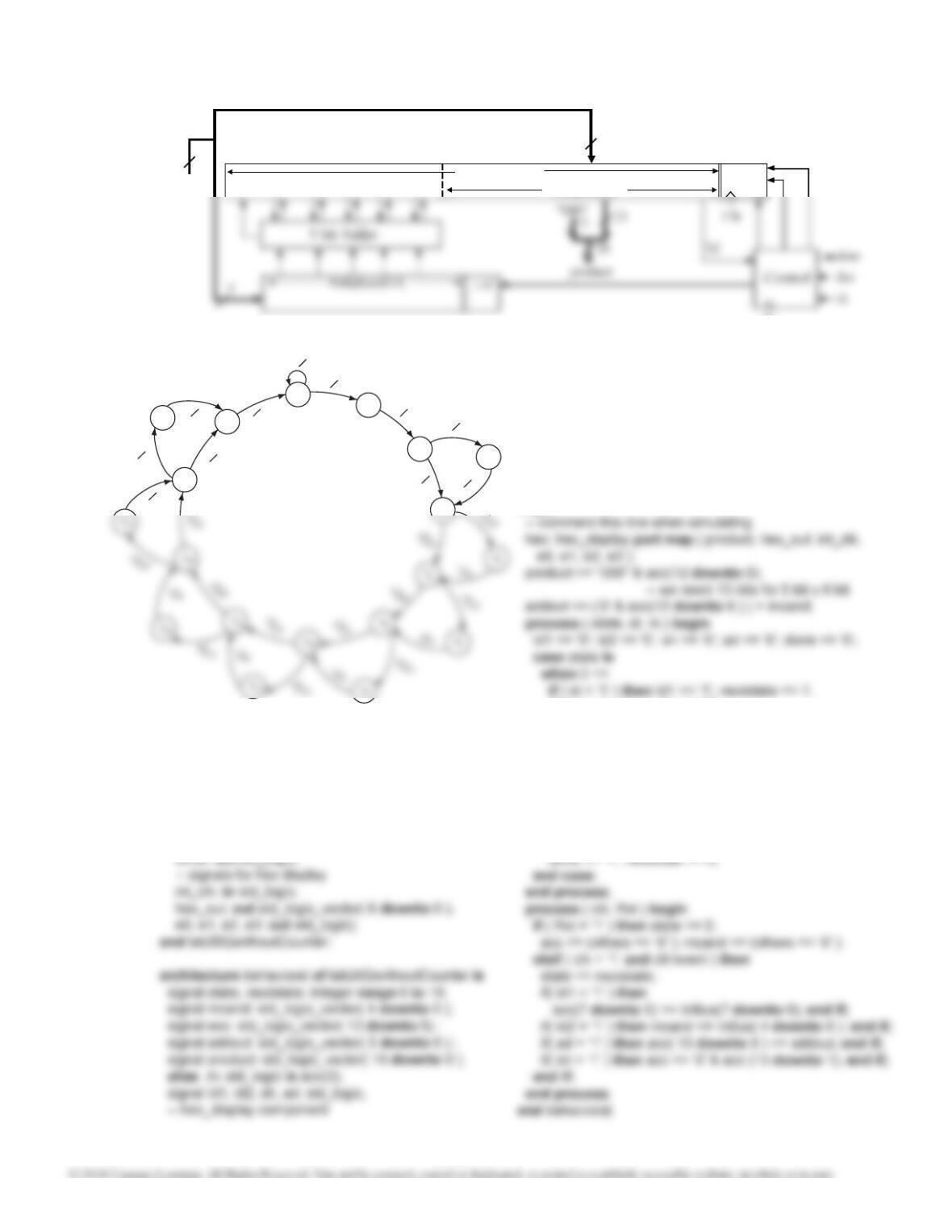

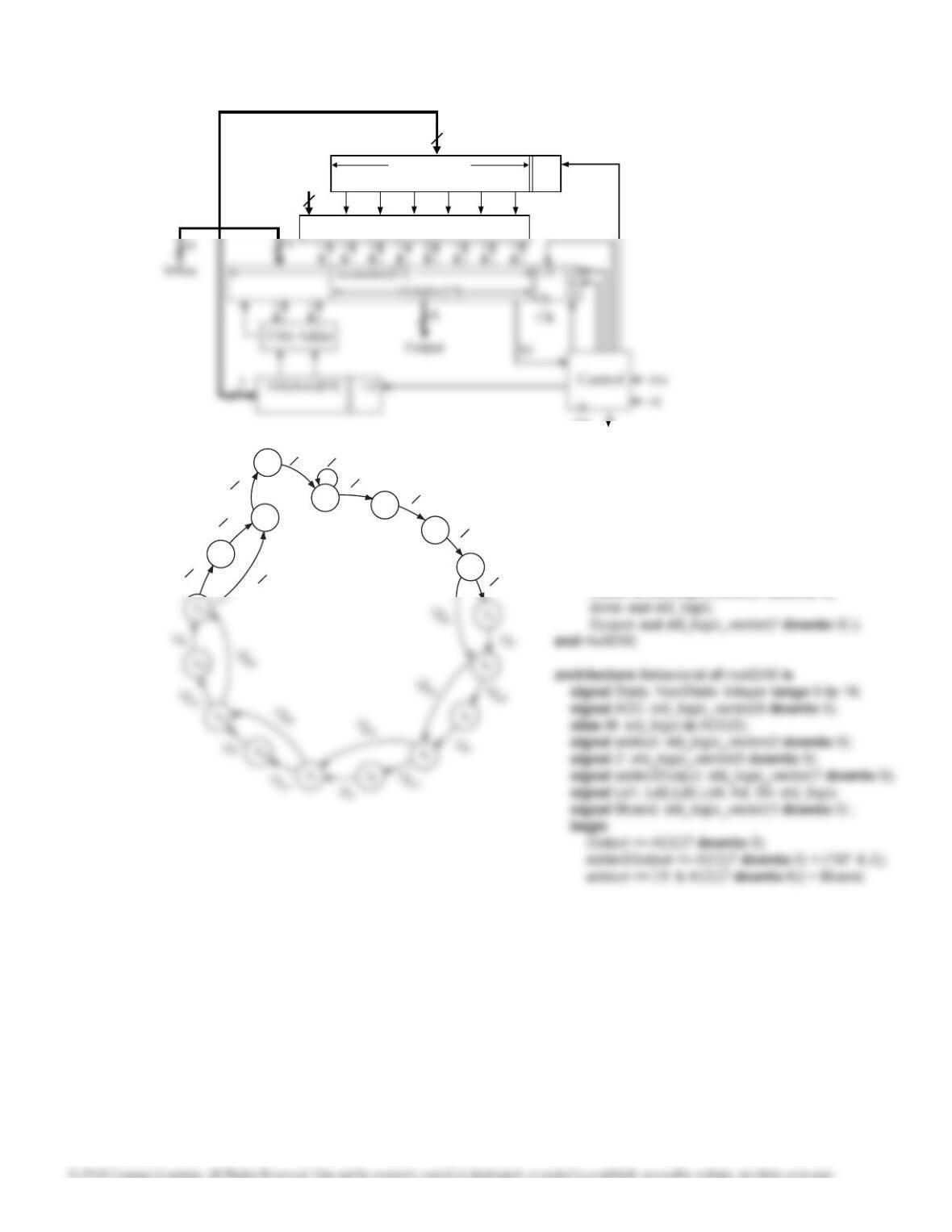

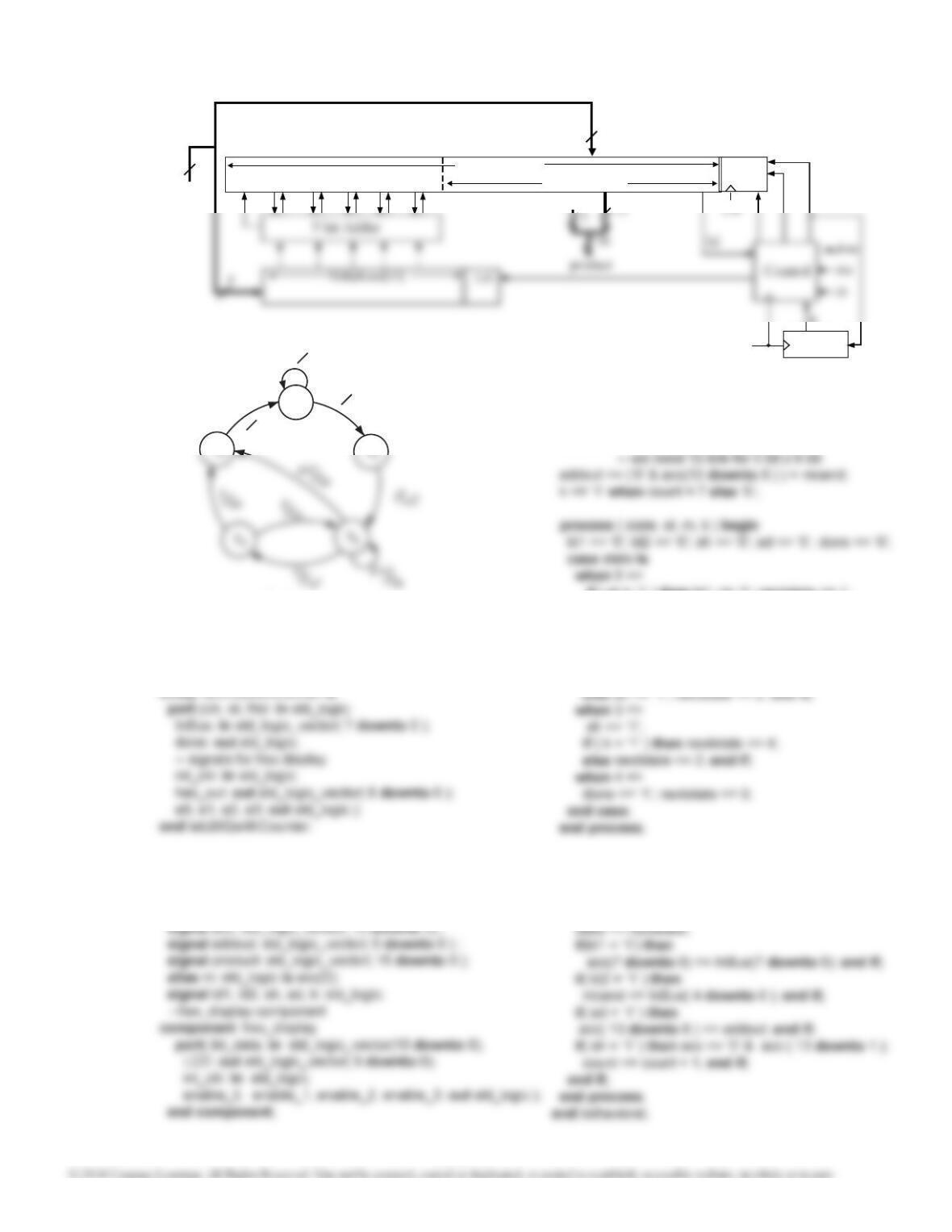

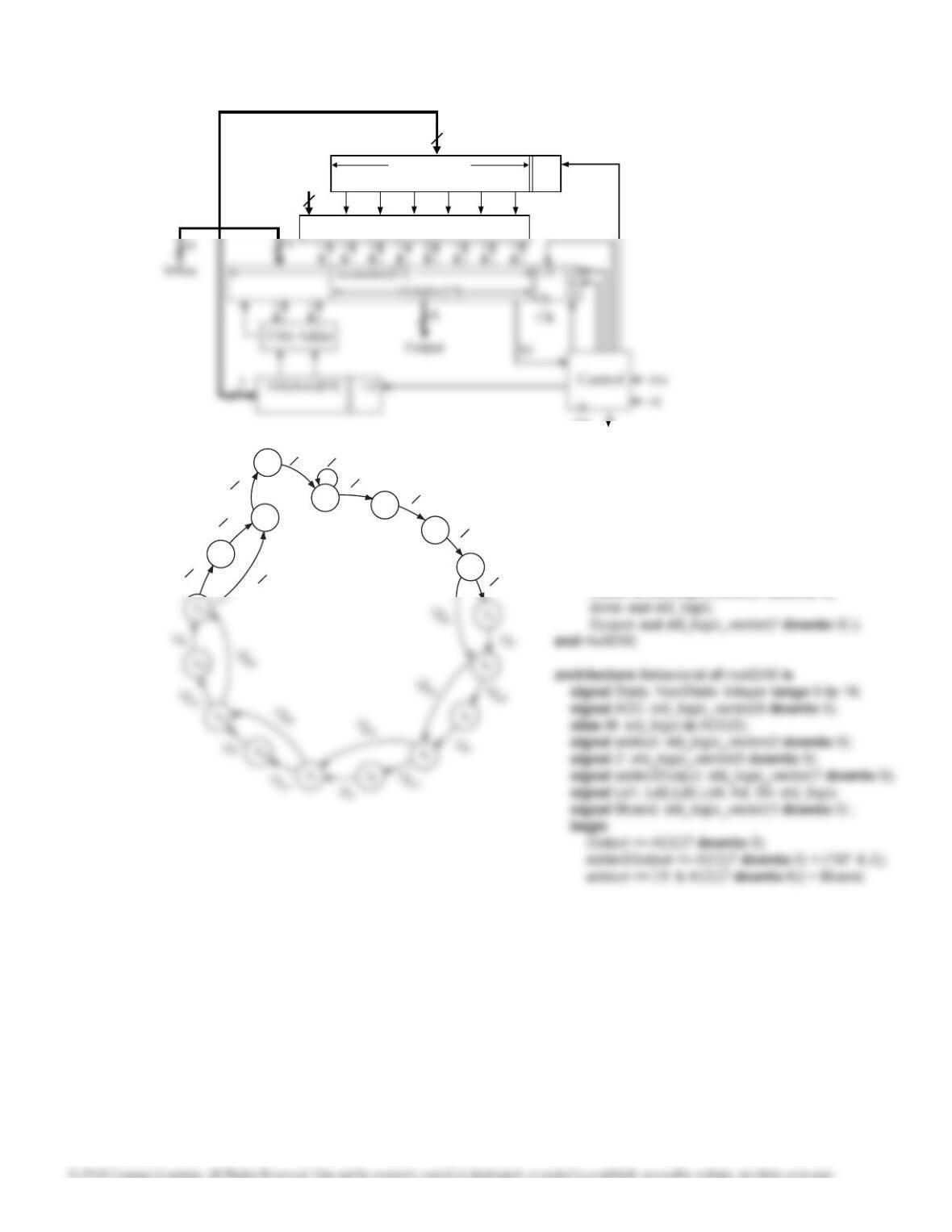

-- 20P with counter (cont.)

begin

-- comment this line when simulating

hex: hex_display port map ( product, hex_out, int_clk,

e0, e1, e2, e3 );

product <= “000” & acc(12 downto 0);

-- we need 13 bits for 8 bit x 5 bit

addout <= (‘0’ & acc(12 downto 5 ) ) + mcand;

k <= ‘1’ when count = 4 else ‘0’;

process ( state, St, M, k ) begin

Ld1 <= ‘0’; Ld2 <= ‘0’; Sh <= ‘0’; Ad <= ‘0’; done <= ‘0’;

case state is

when 0 =>

if ( k = ‘1’ ) then nextstate <= 4;

else nextstate <= 2; end if;

when 4 => done <= ‘1’; nextstate <= 0;

end case;

end process;

process ( Clk, Rst ) begin

if ( Rst = ‘1’ ) then state <= 0; count <= “000”;

acc <= (others => ‘0’ ); mcand <= (others => ‘0’ );