Unit 16 Design Solutions

303

Solutions to Unit 16 Design and Simulation Problems

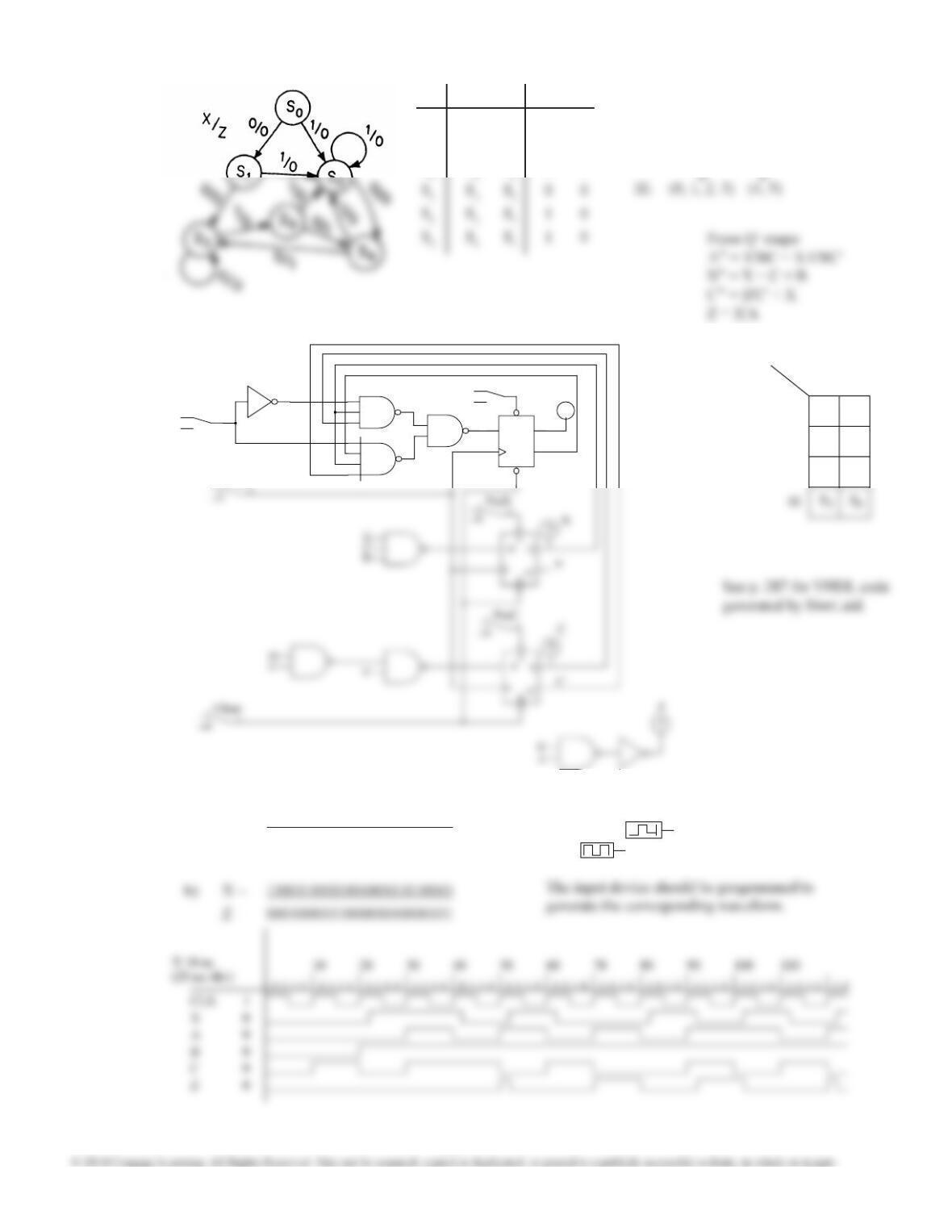

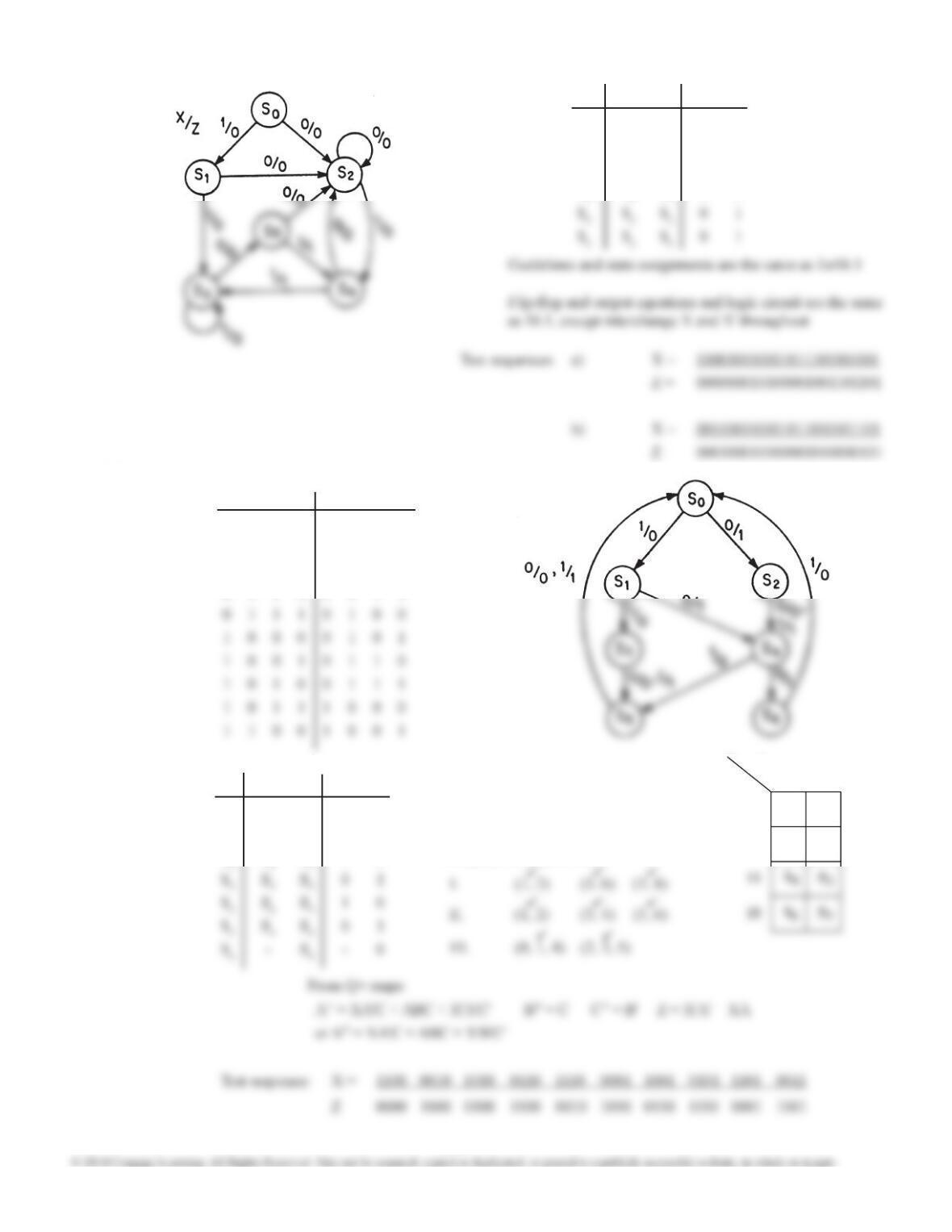

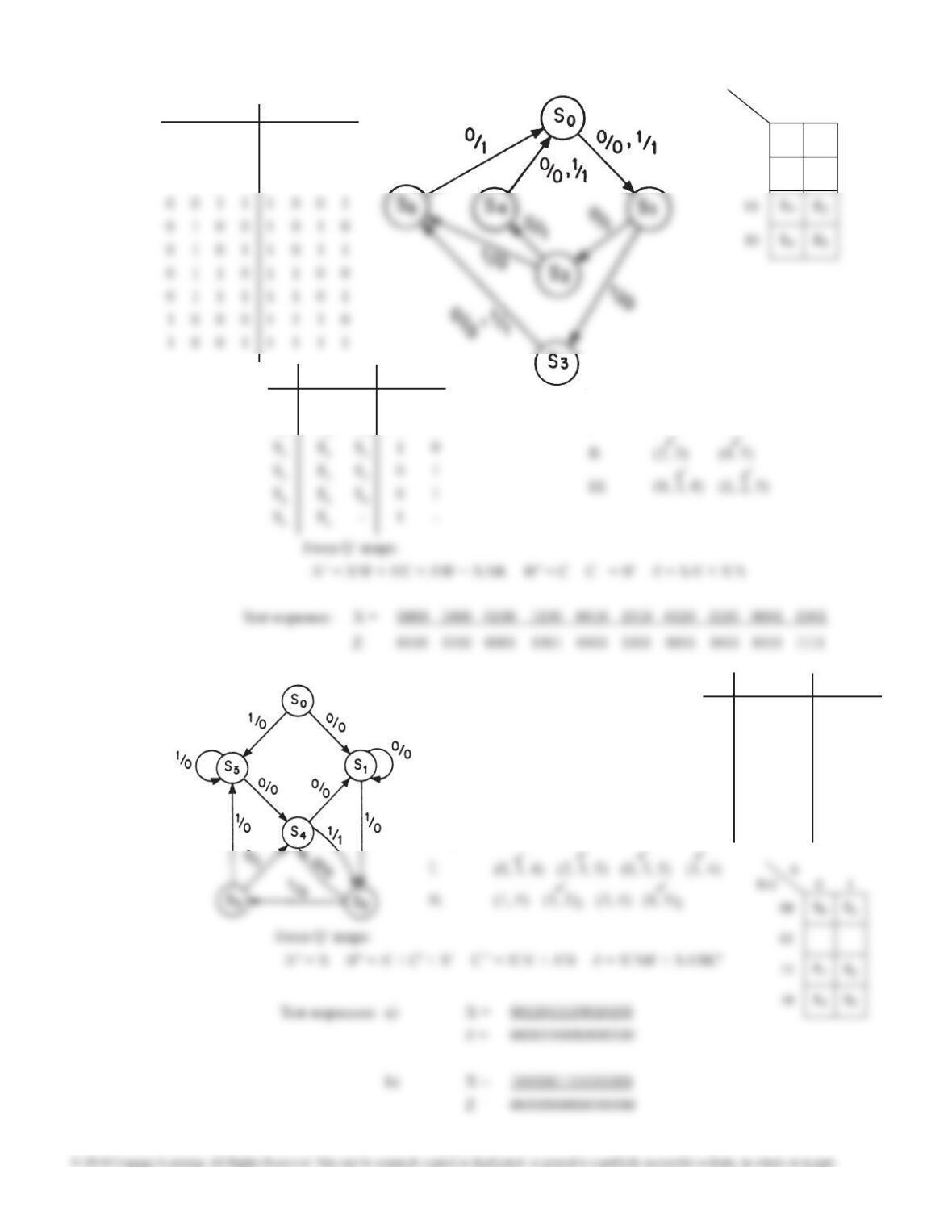

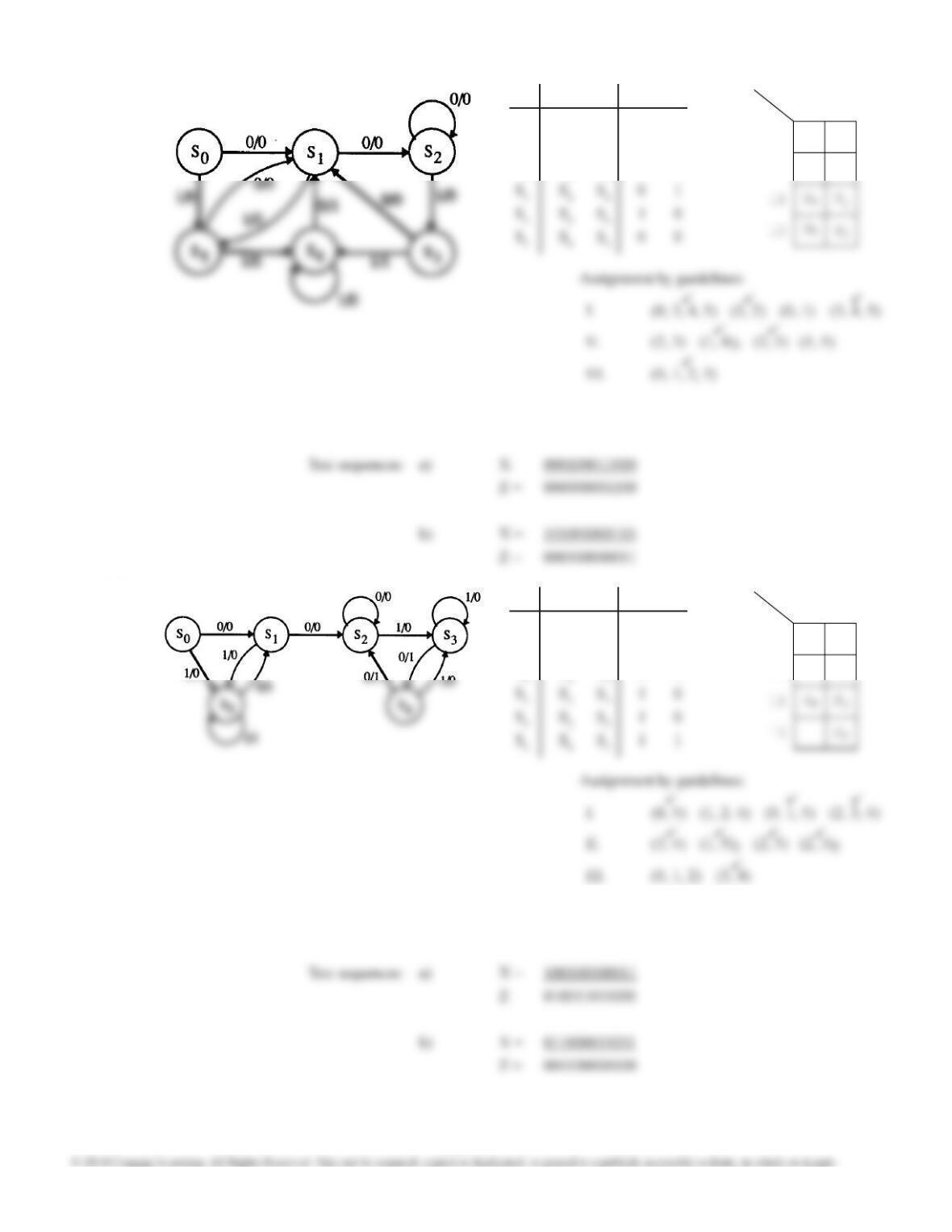

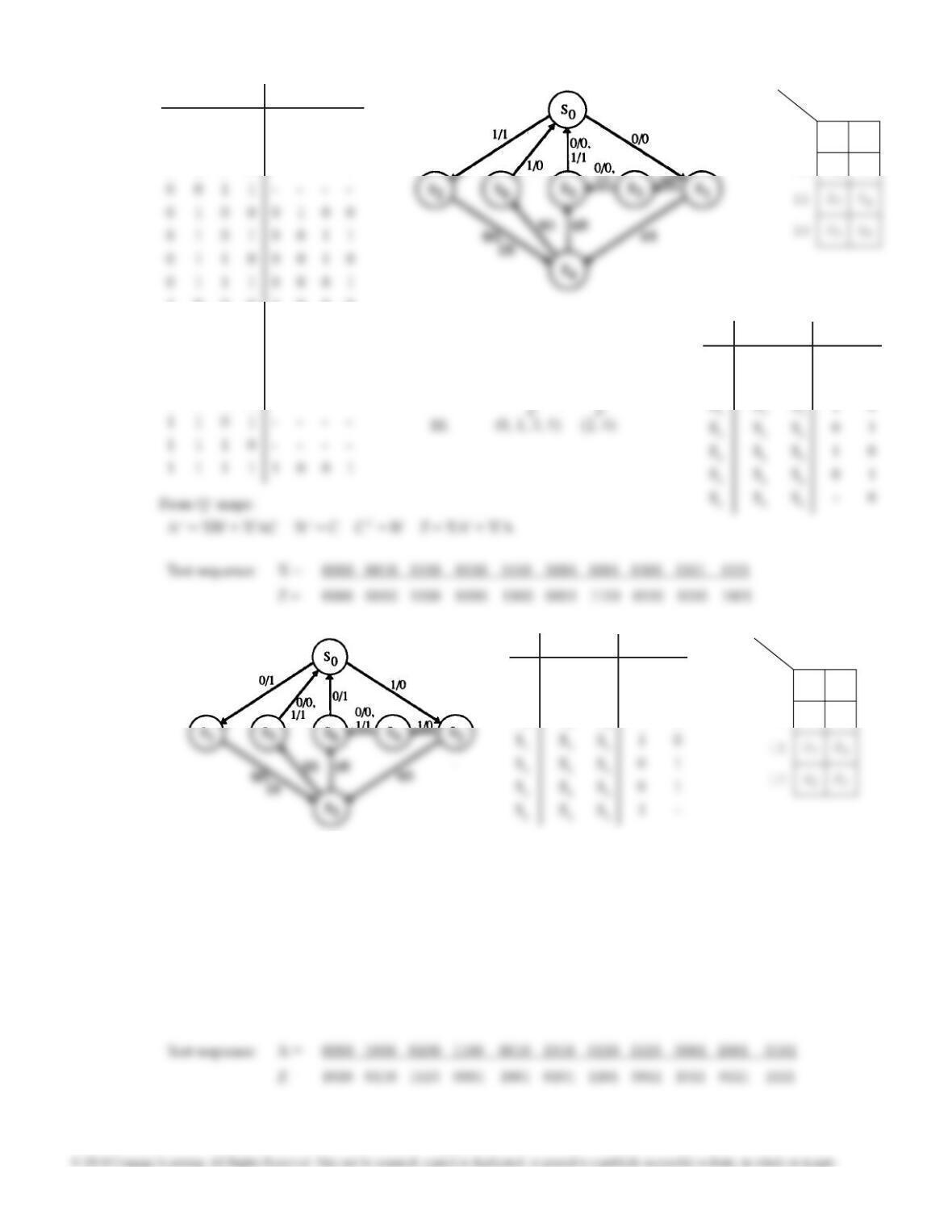

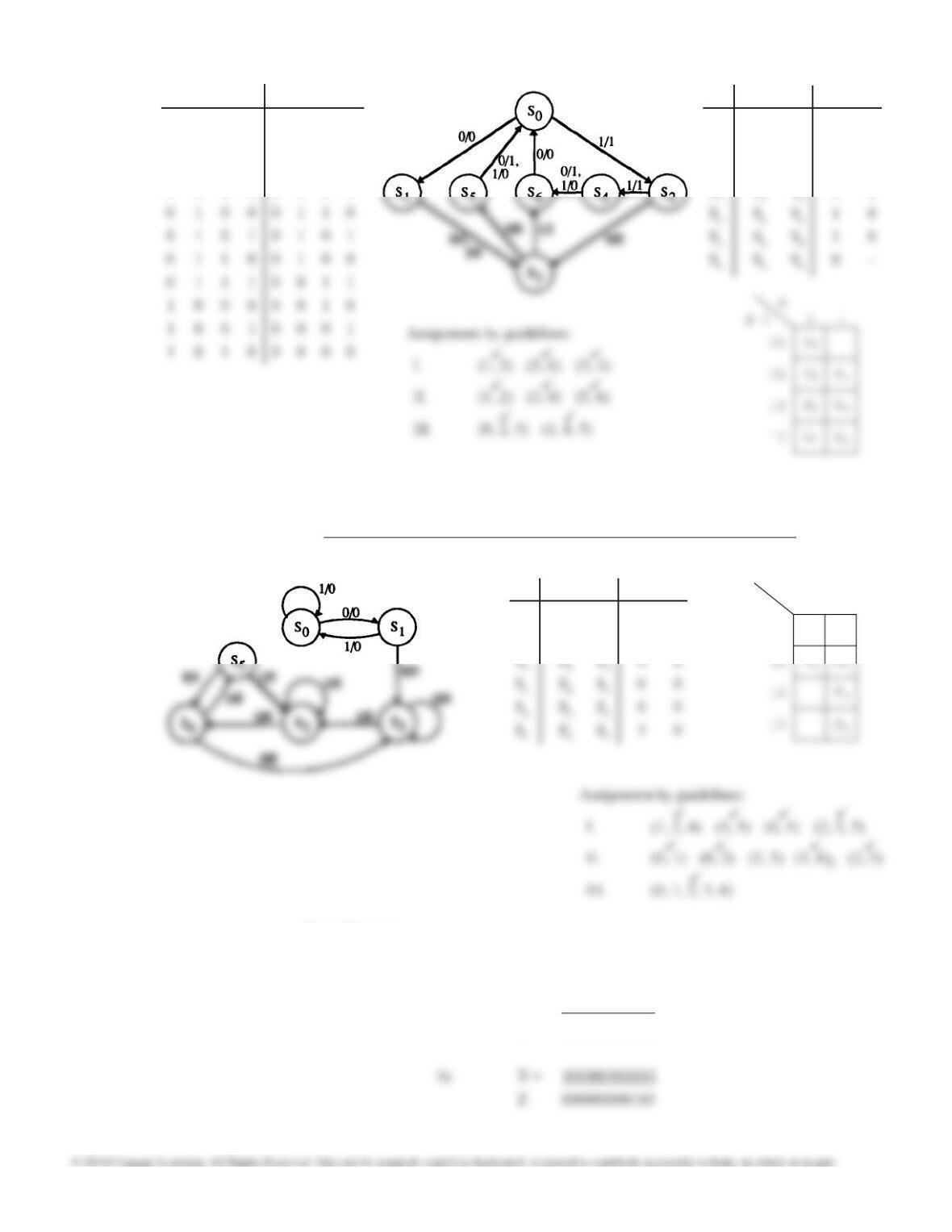

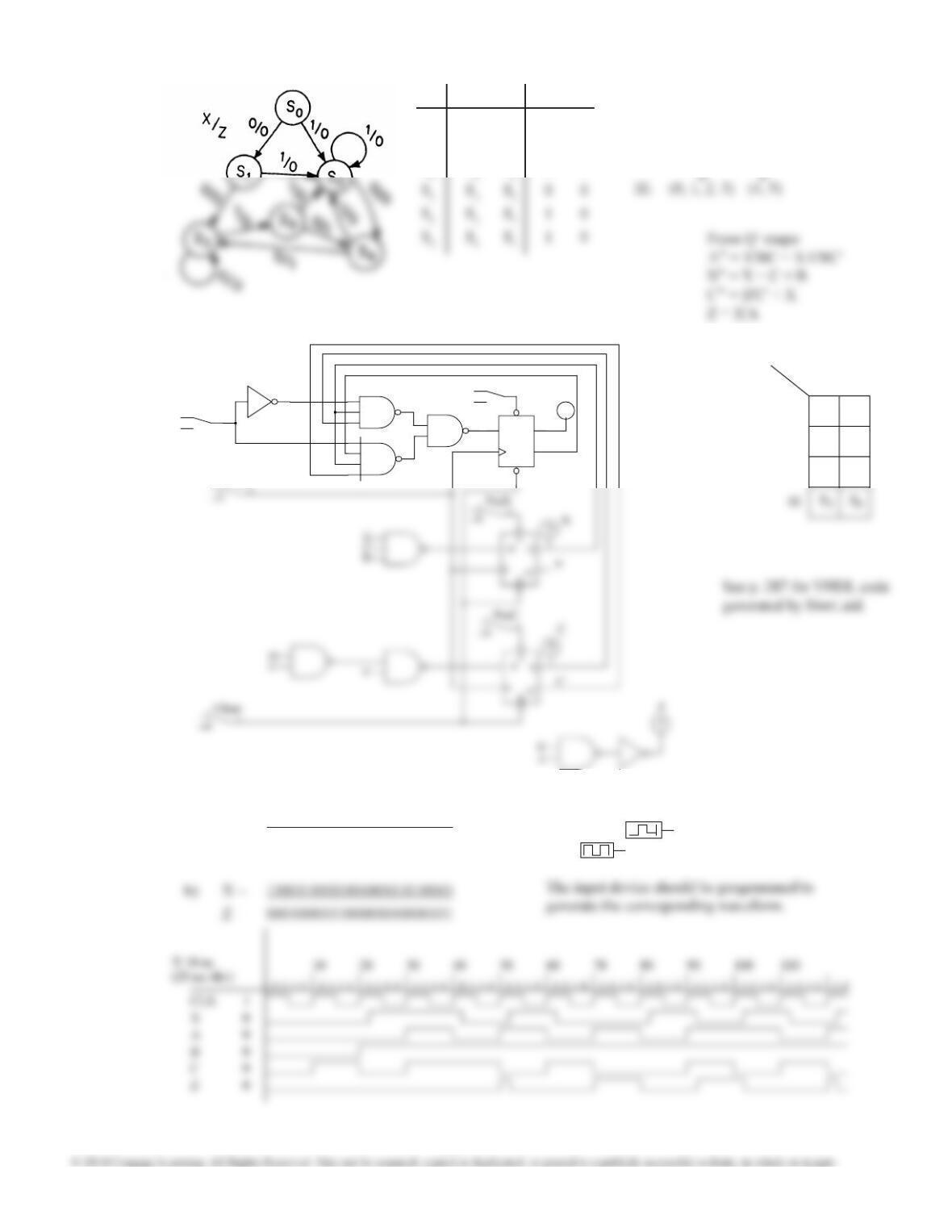

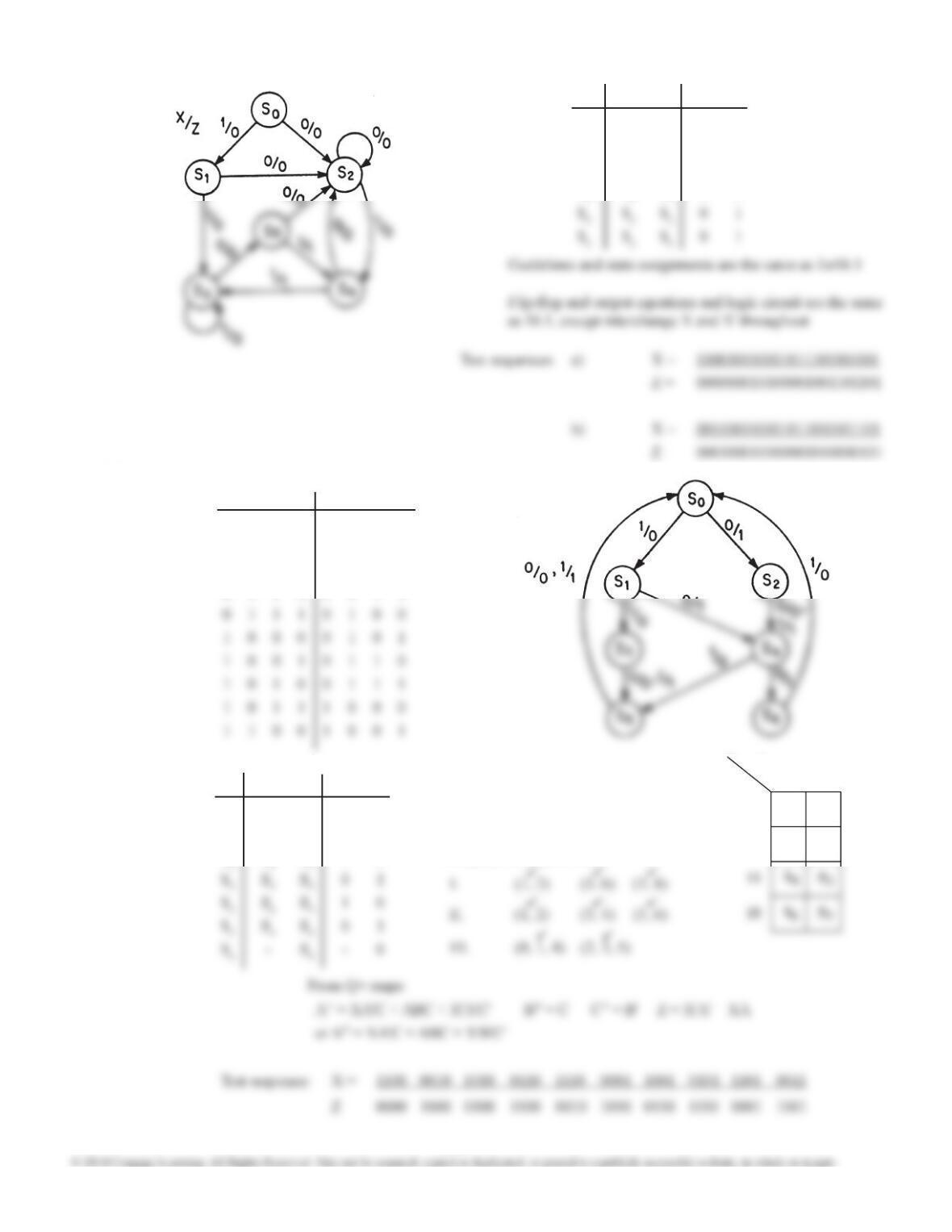

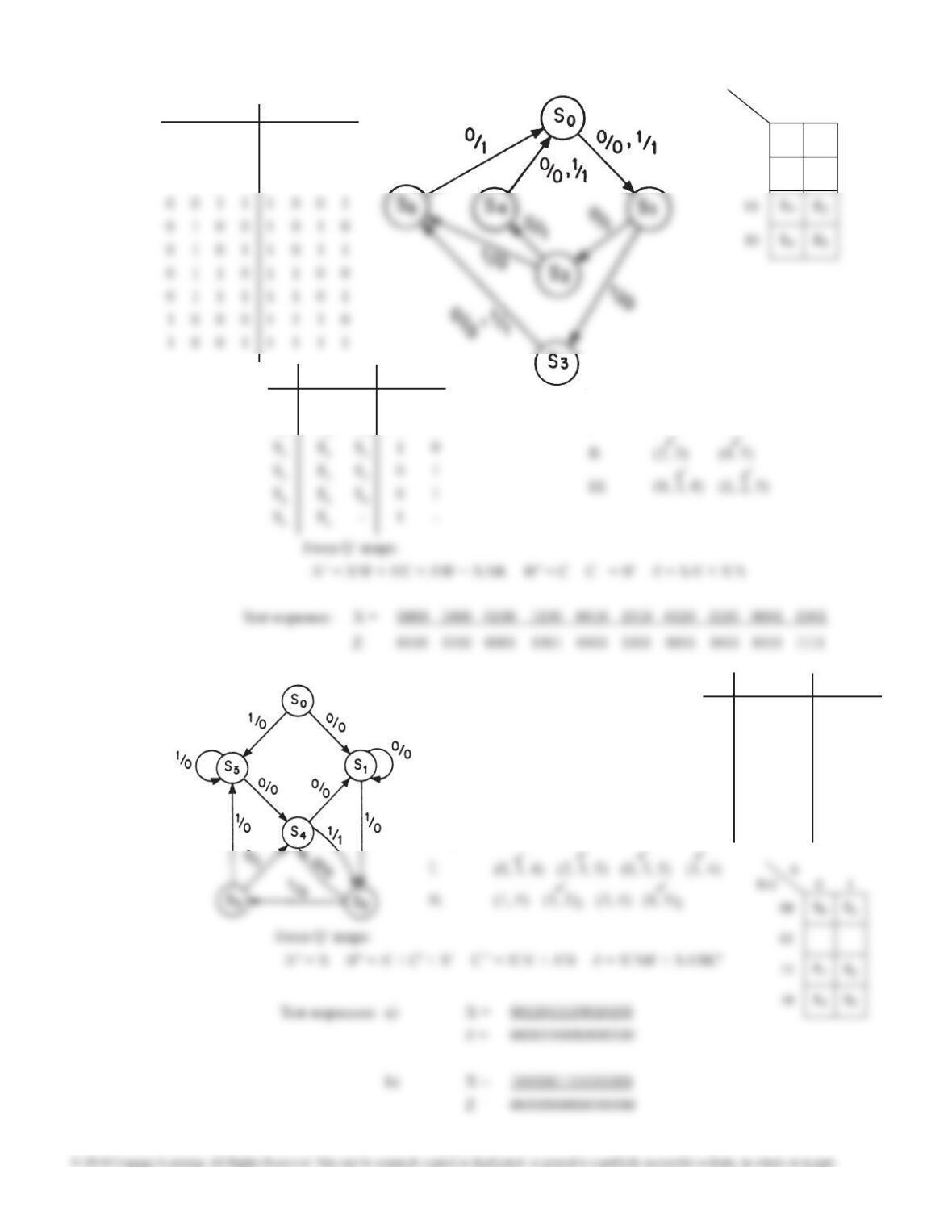

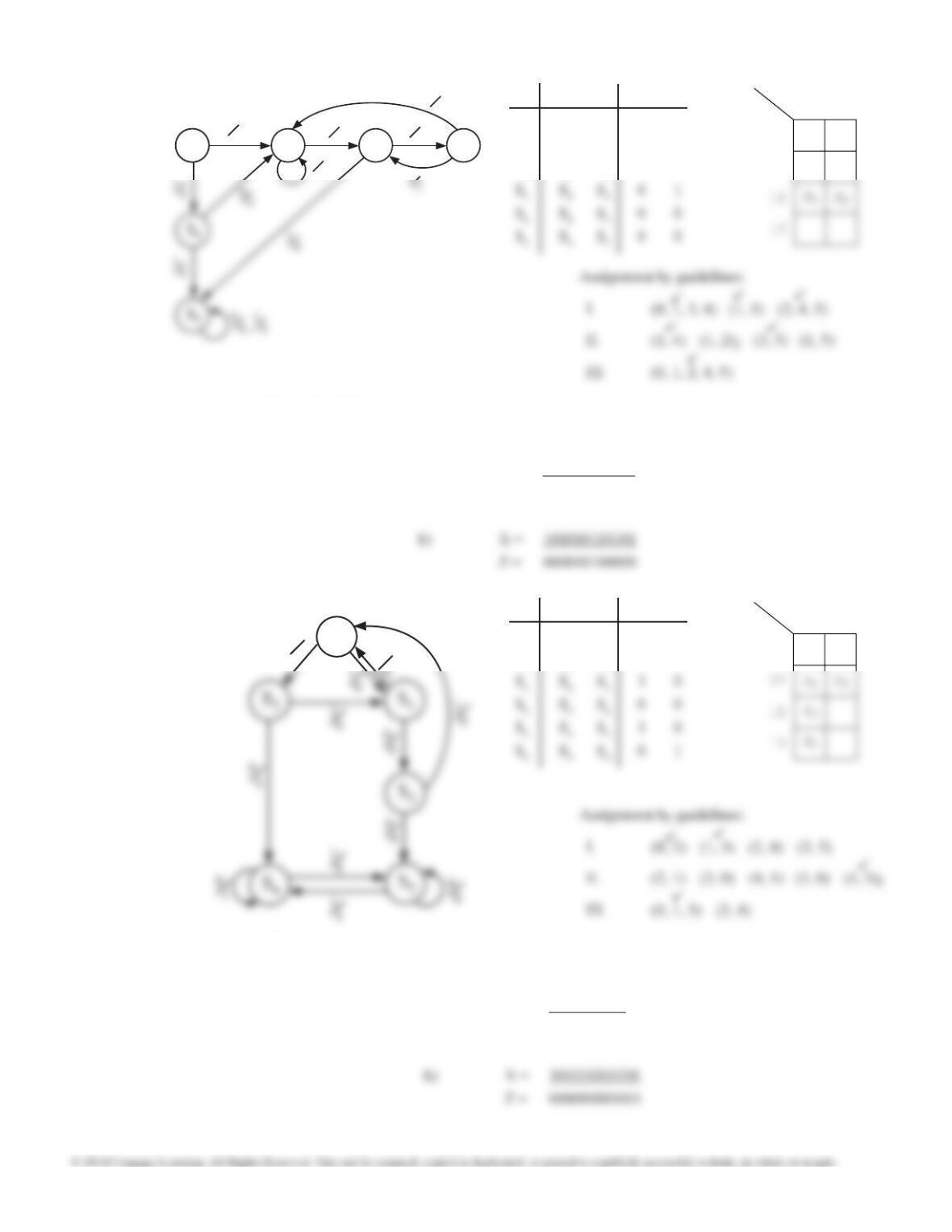

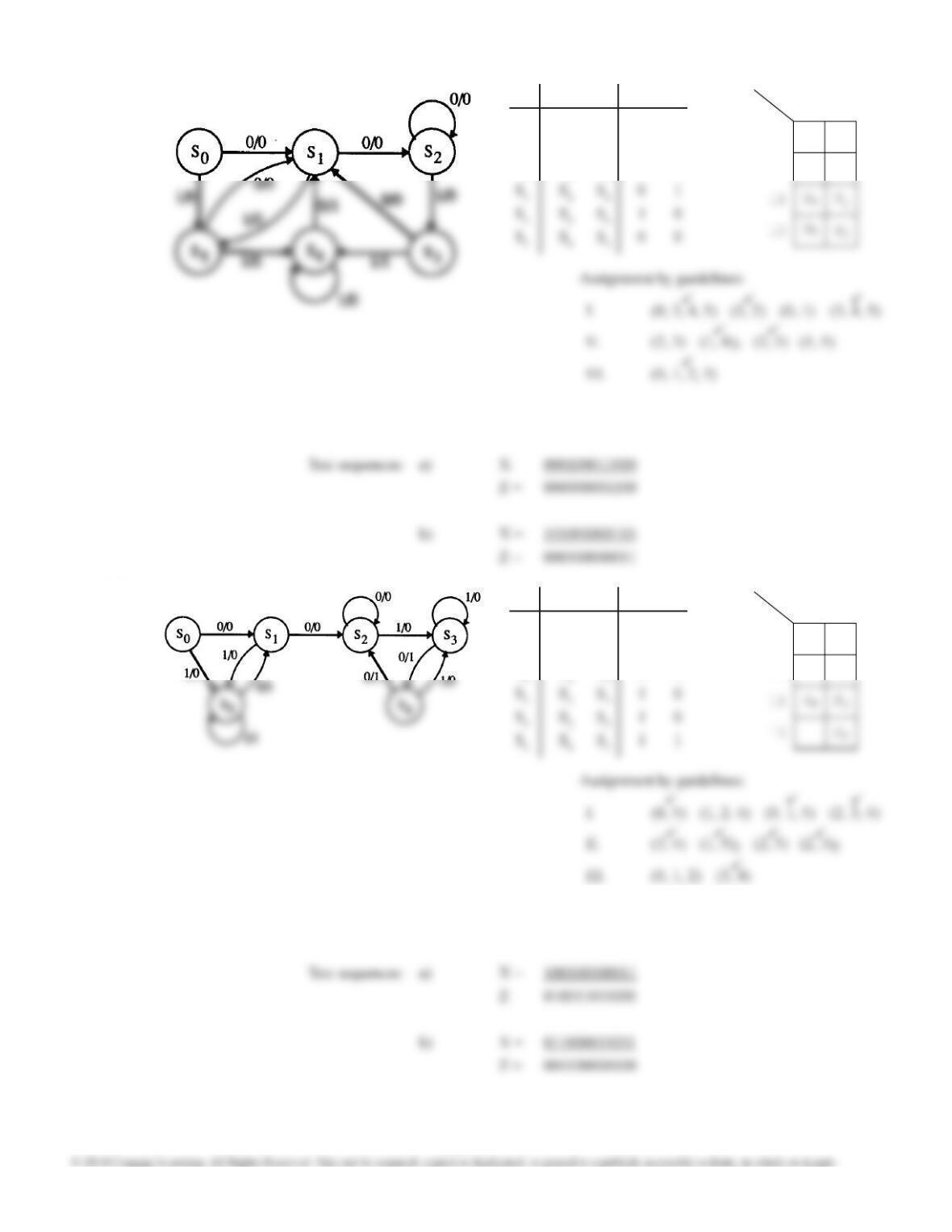

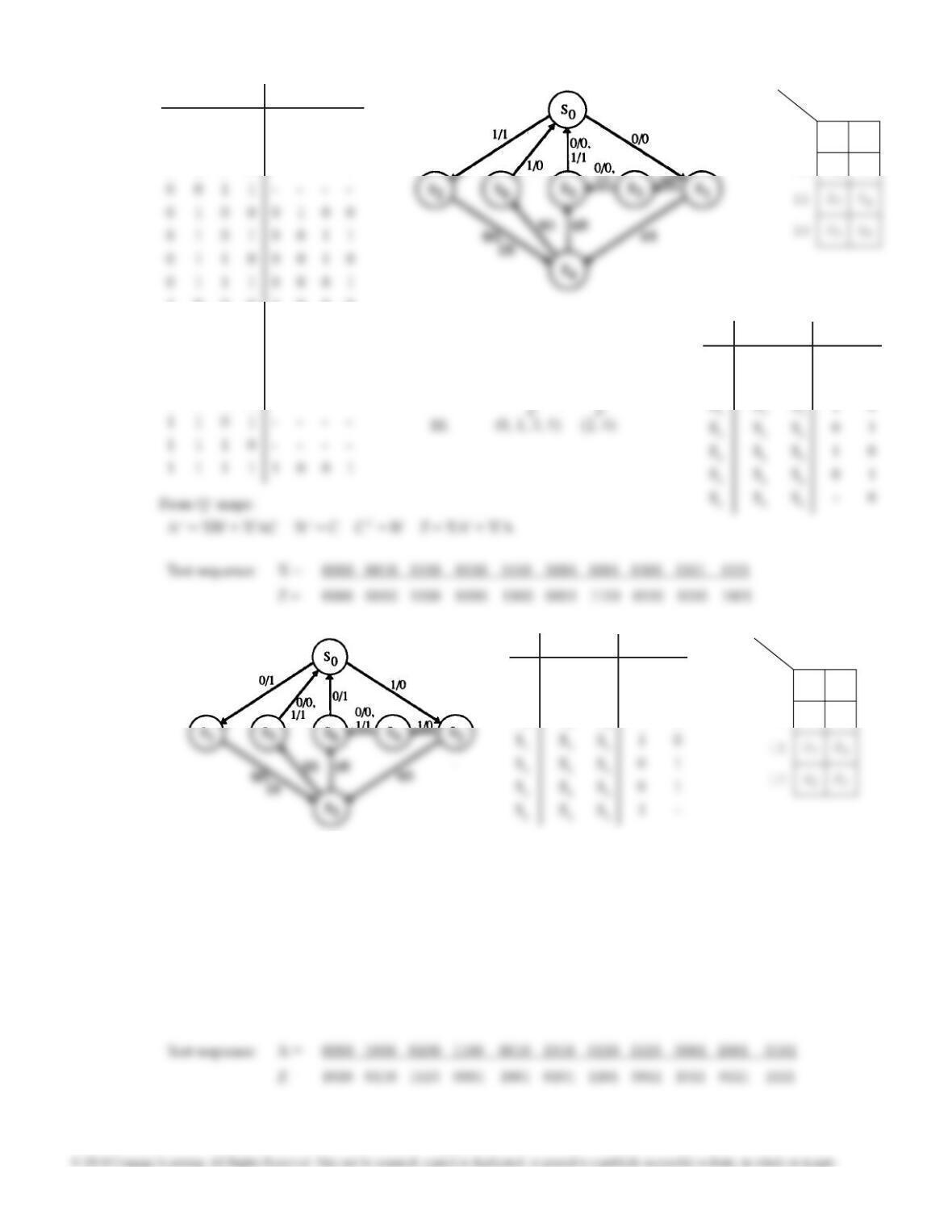

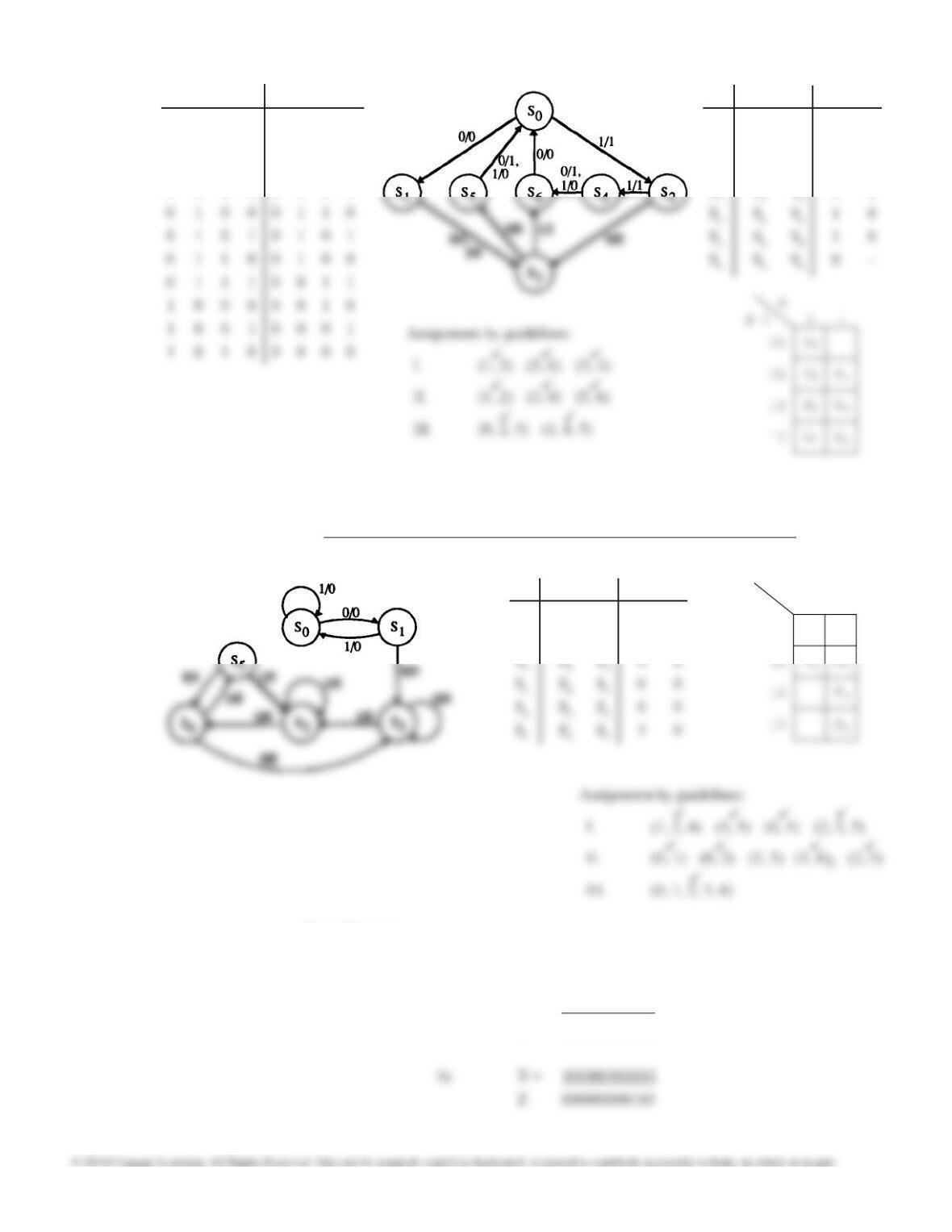

Problems 16.1 through 16.14 are Mealy sequential circuit design and simulation problems. These problems are of

approximately equal difficulty so that different students can be assigned different problems. In this exercise, students

first complete their designs using gates and D ip-ops. They then test their designs using the SimUaid simulator.

Next, they convert their design to VHDL, synthesize the VHDL code, and download it to a CPLD or FPGA board to

test their design using hardware.

We ask our students to use the following procedure:

(1) Derive a state graph and state table for the assigned problem. Reduce the table to a minimum number of

states. Check the reduced table using the LogicAid state table checker. Encoded solution files are found in

the Lab16 folder on the CD.

(2) Make a state assignment using the guidelines. Derive the transition table, and then derive the D ip-op

input equations and output equation(s) using Karnaugh maps.

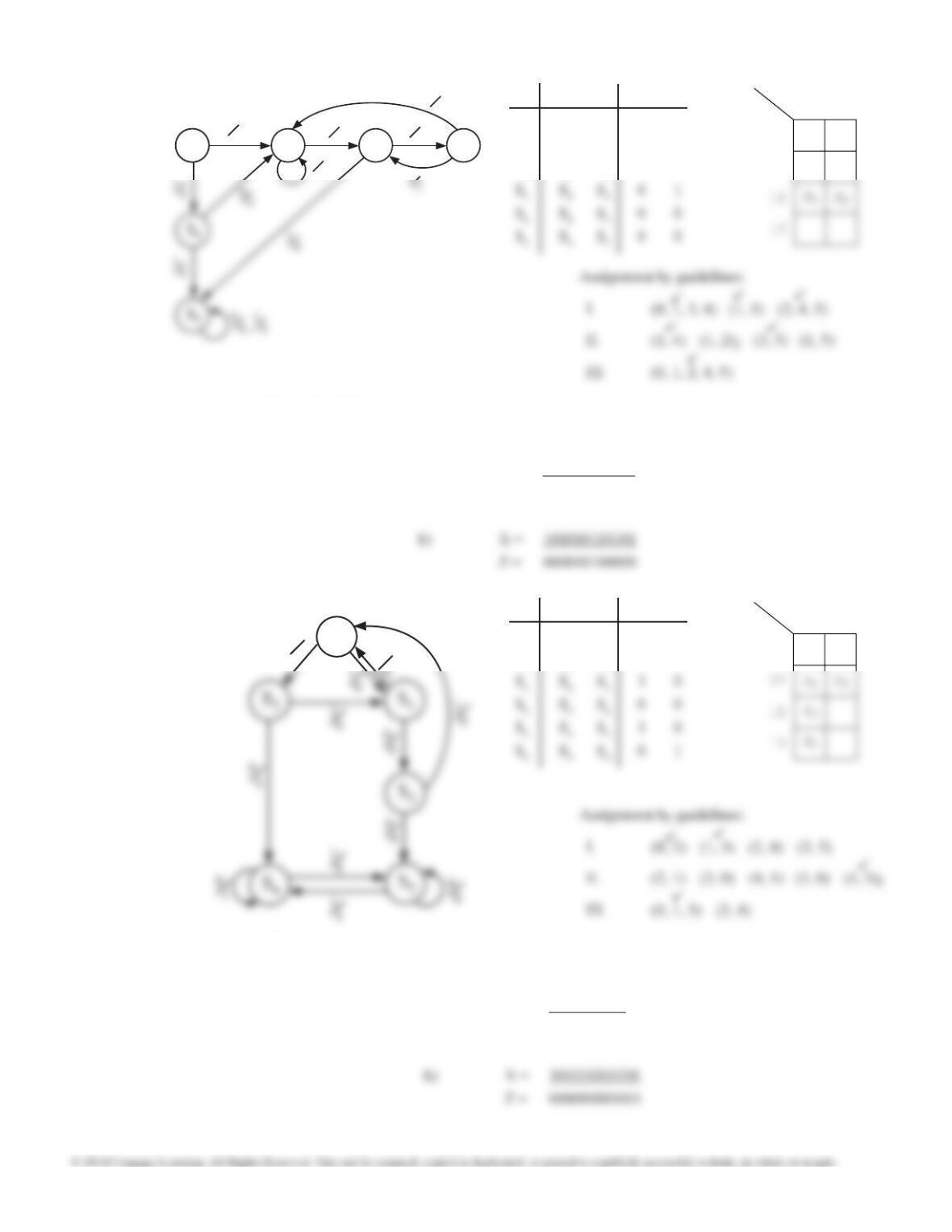

operation of the circuit by applying the required test sequences and observing the outputs, being very careful

to read the outputs at the proper time.

(6) Replace the clock and X input switches with a clock module and an input device. Program the input device

to produce the proper test waveform. Display the simulator timing waveforms for clock, X, Z, and the ip-

op outputs. Print the waveforms and mark the times to read the Z output. Verify that the output sequence

After a proctor has verified that your design is correct and meets specifications, you will implement your design in

hardware using the following steps:

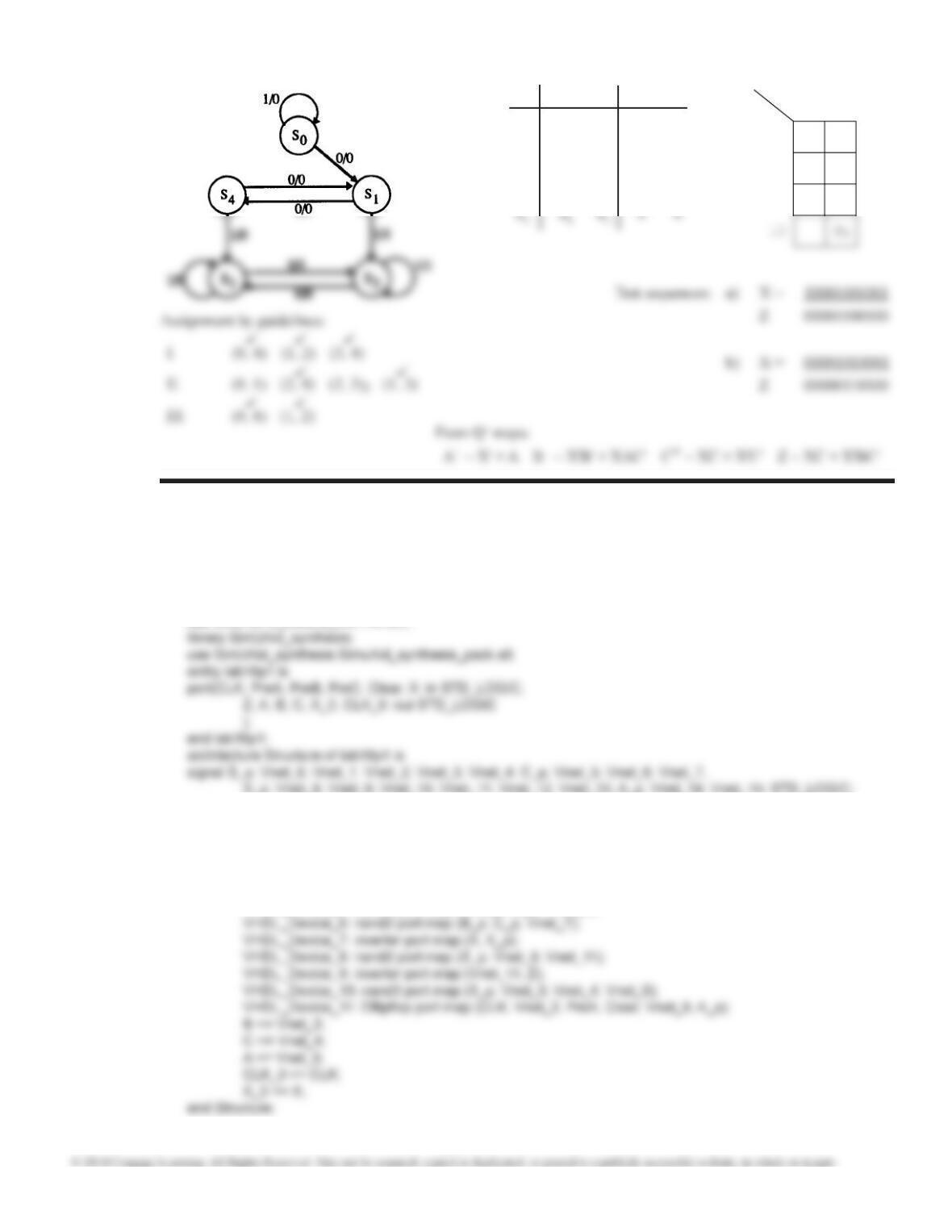

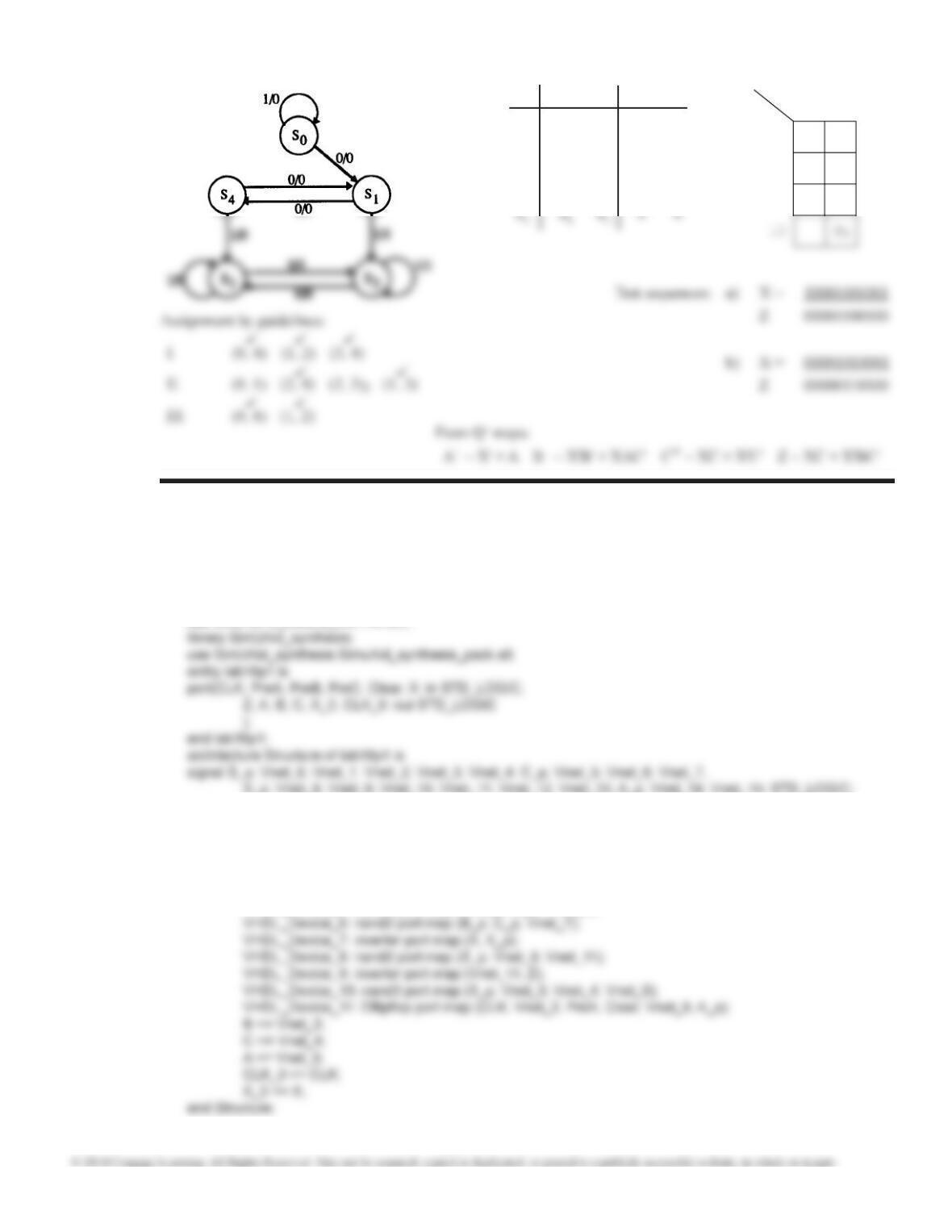

(6) Use SimUaid to generate a VHDL file from your circuit file.

(7) Use the Xilinx ISE software to synthesize the circuit from the VHDL file.

The solution for 16.1 includes the complete SimUaid circuit and the VHDL code generated by SimUaid. The other

solutions only give the logic equations for the ip-op inputs and for Z.