Unit 13 Solutions

153

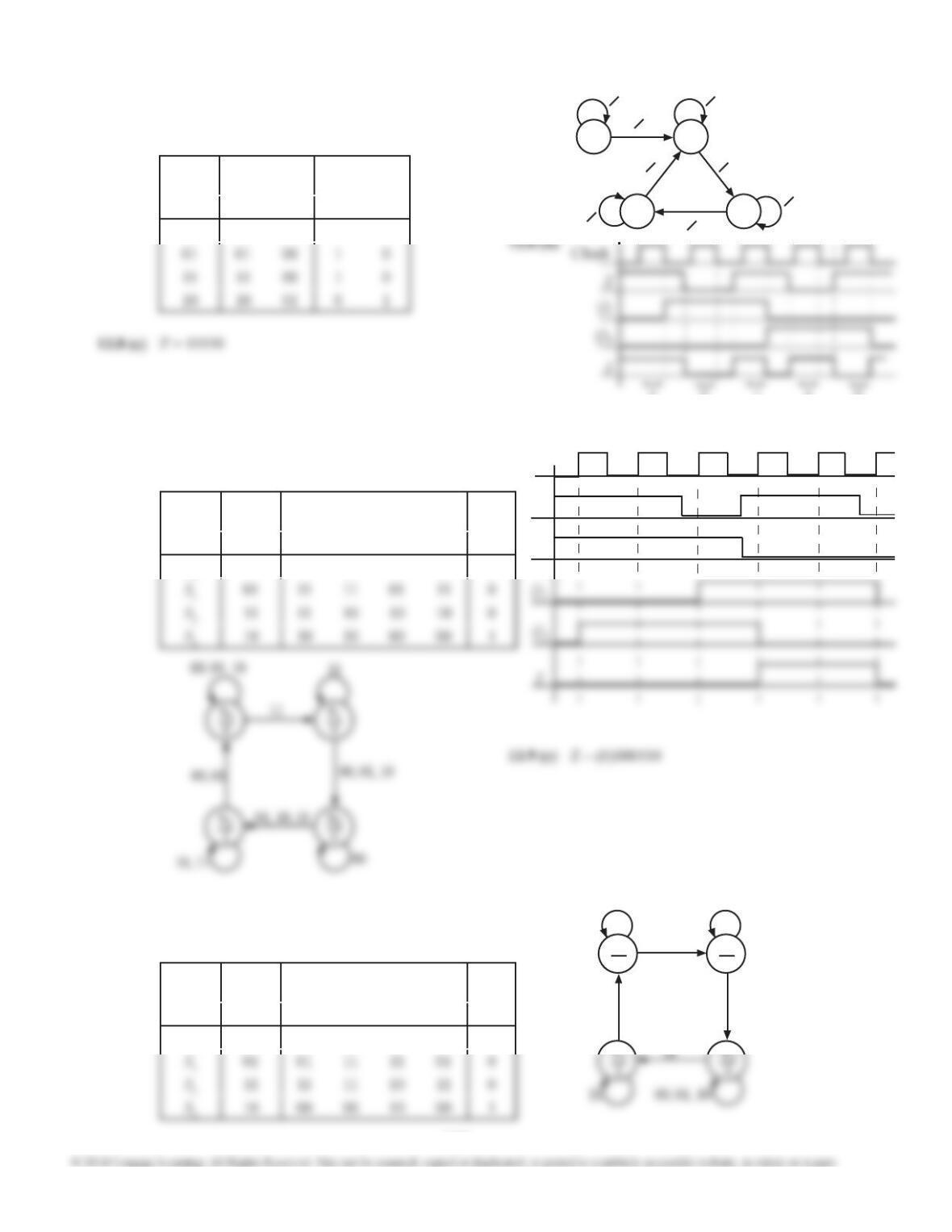

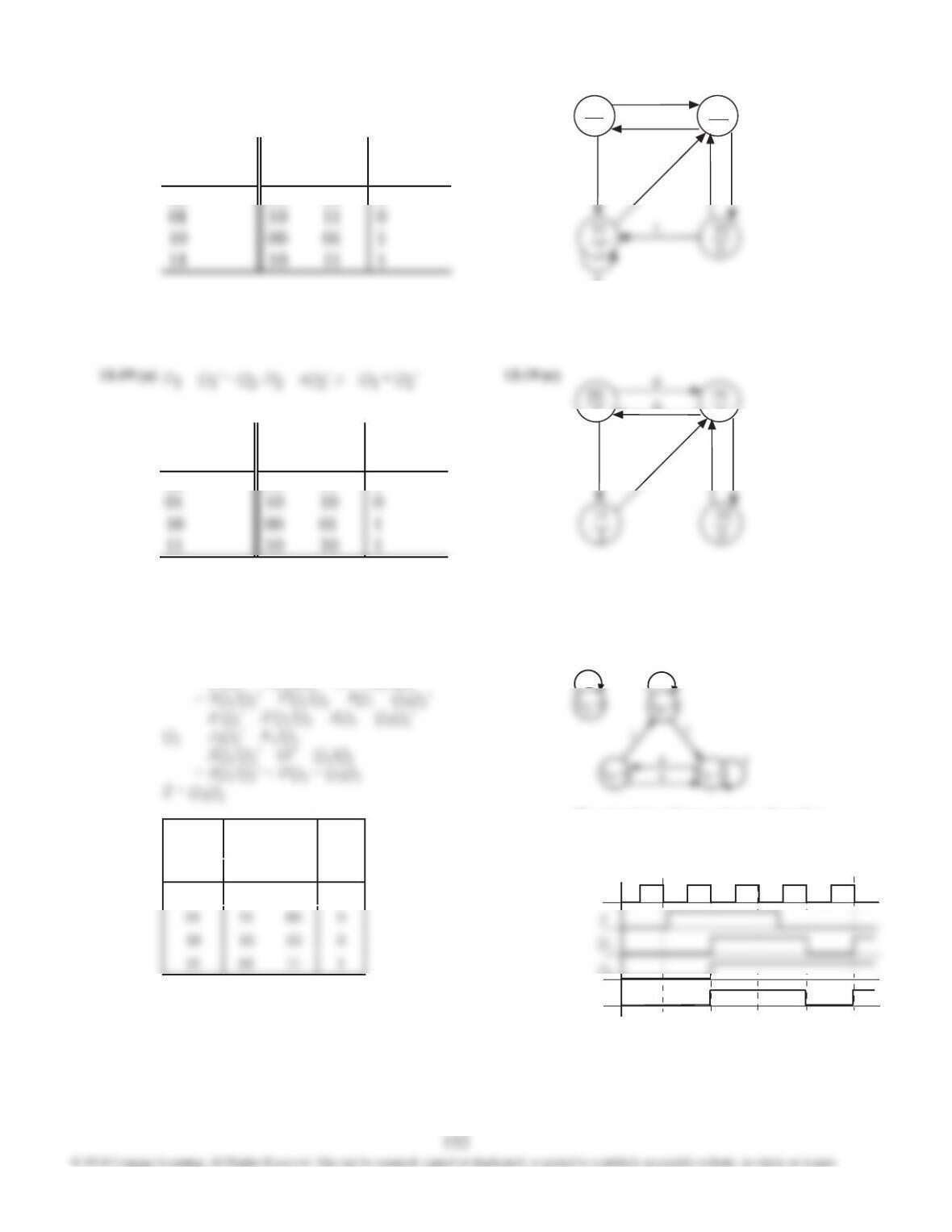

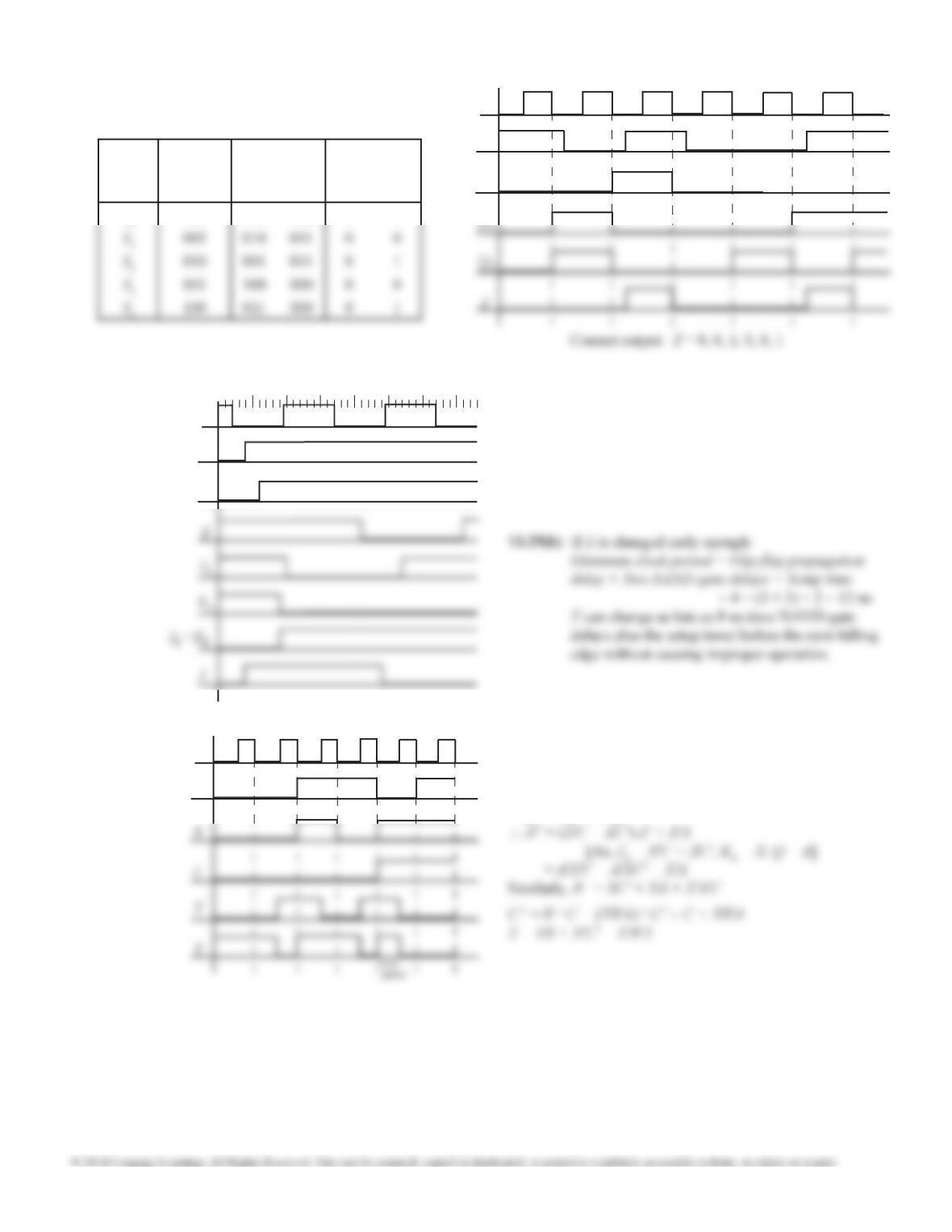

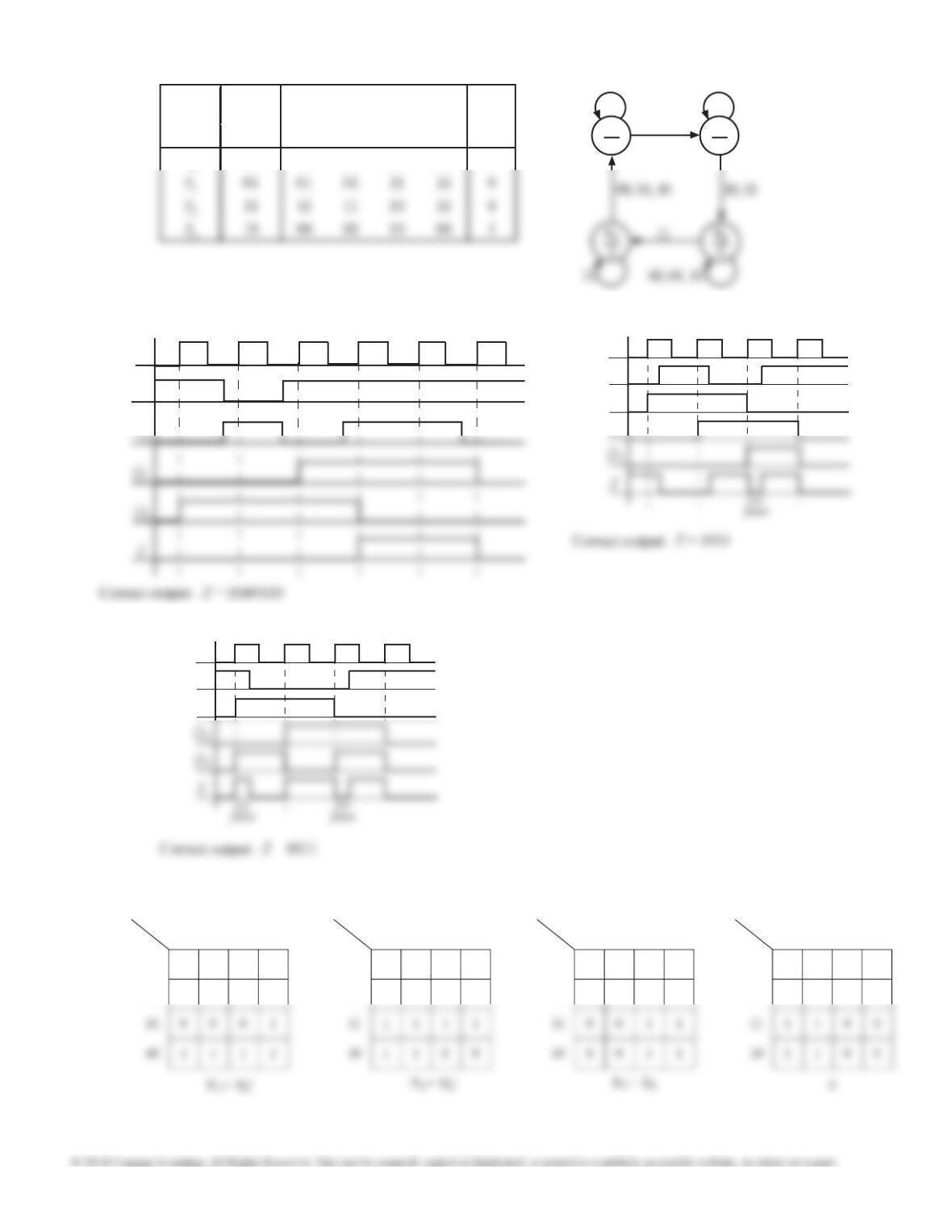

13.21 Clock Cycle Information Gathered

1Q1Q2 = 00, X = 0 ⇒ Z = 1, Q1

+Q2

+ = 01

2Q1Q2 = 01, X = 0 ⇒ Z = 0; X = 1 ⇒ Z = 1, Q1

+Q2

+ = 11

3Q1Q2 = 11, X = 1 ⇒ Z = 1; X = 0 ⇒ Z = 0, Q1

+Q2

+ = 10

Present

State

Next State

Q1

+Q2

+Z

Q1Q2X = 0 X = 1 X = 0 X = 1

00 01 10 1 0

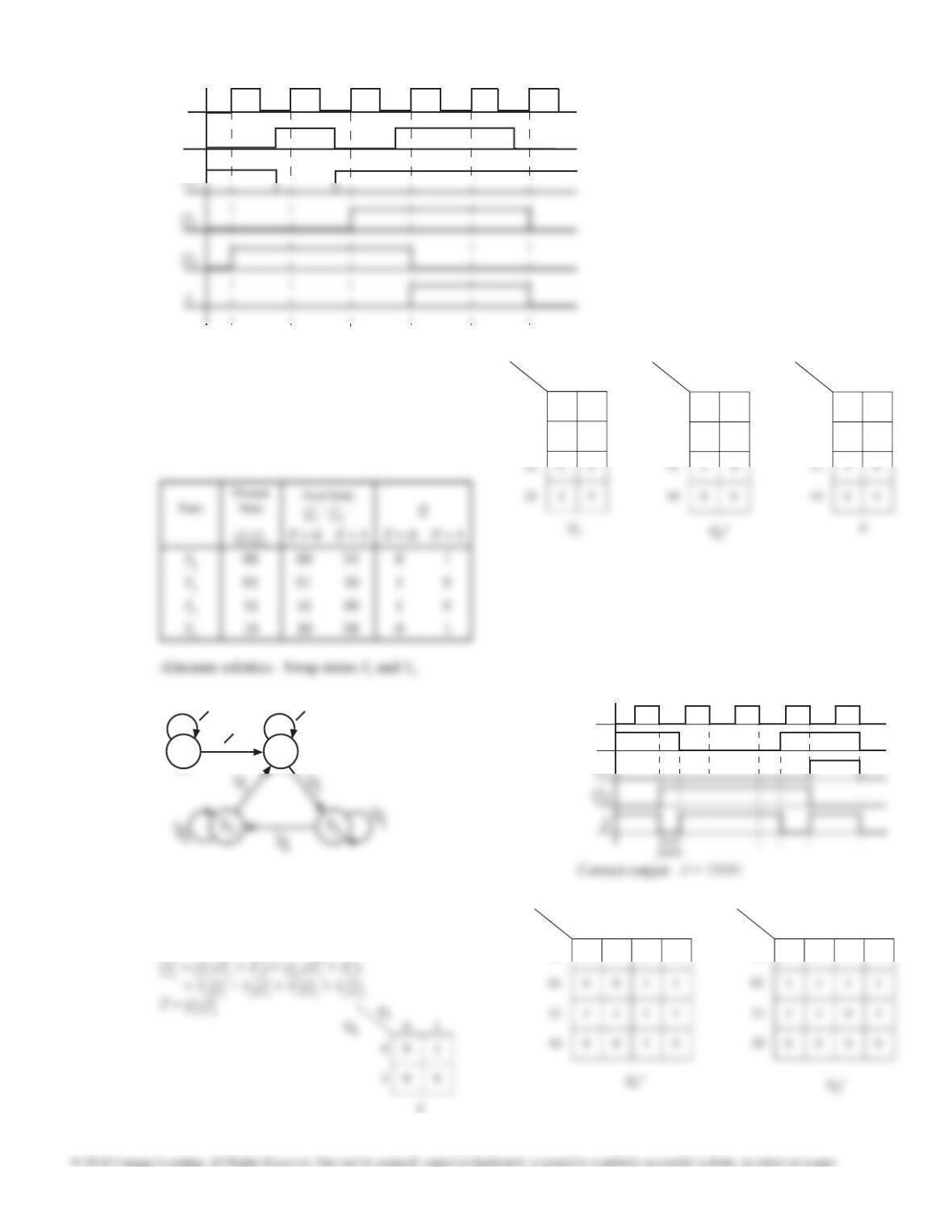

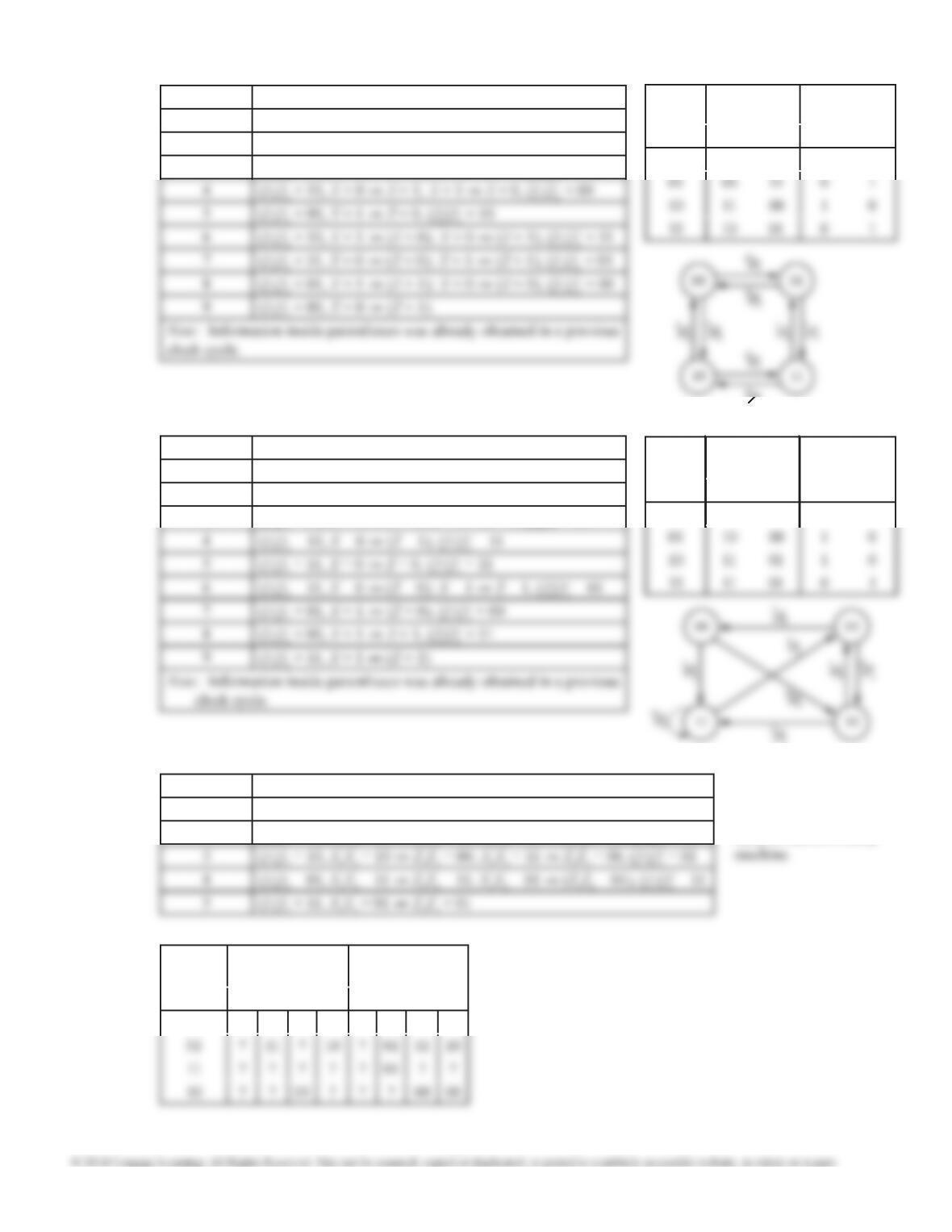

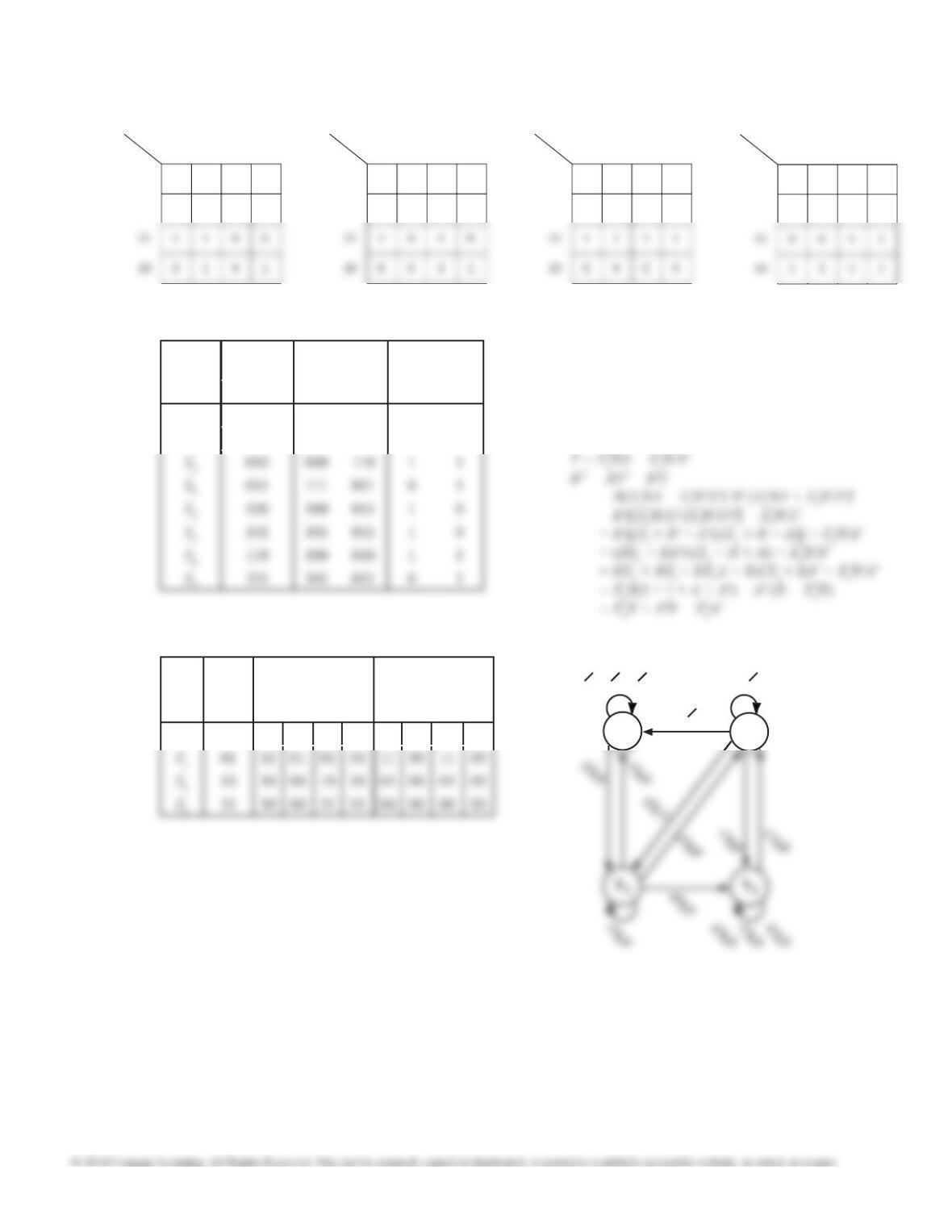

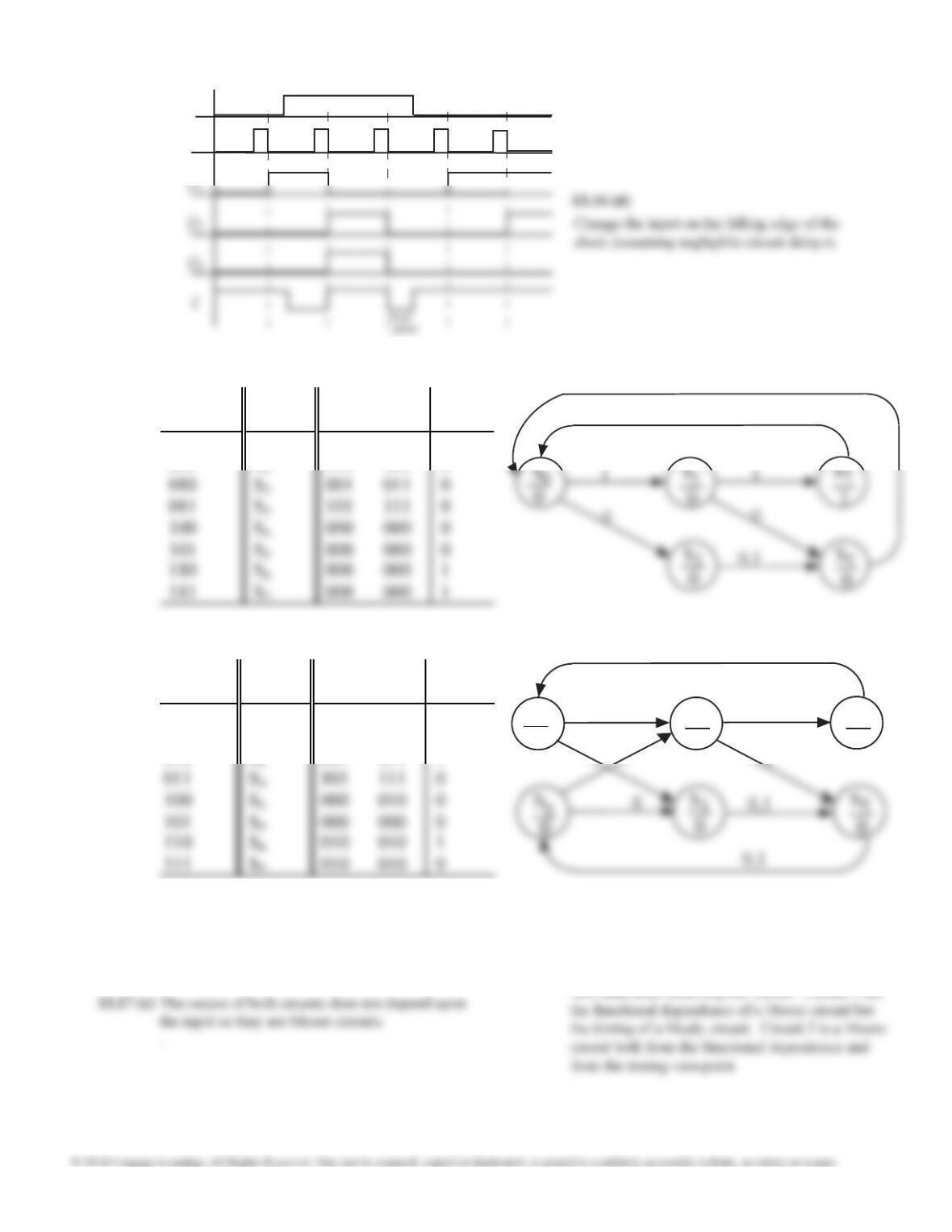

13.22 Clock Cycle Information Gathered

1Q1Q2 = 00, X = 0 ⇒ Z = 0, Q1

+Q2

+ = 10

2Q1Q2 = 10, X = 0 ⇒Z = 1; X = 1⇒ Z = 0, Q1

+Q2

+ = 01

3Q1Q2 = 01, X = 1 ⇒ Z = 0; X = 0⇒ Z = 1, Q1

+Q2

+ = 10

Present

State

Next State

Q1

+Q2

+Z

X = 0 X = 1

Q1Q2X = 0 X = 1

00 10 11 0 1

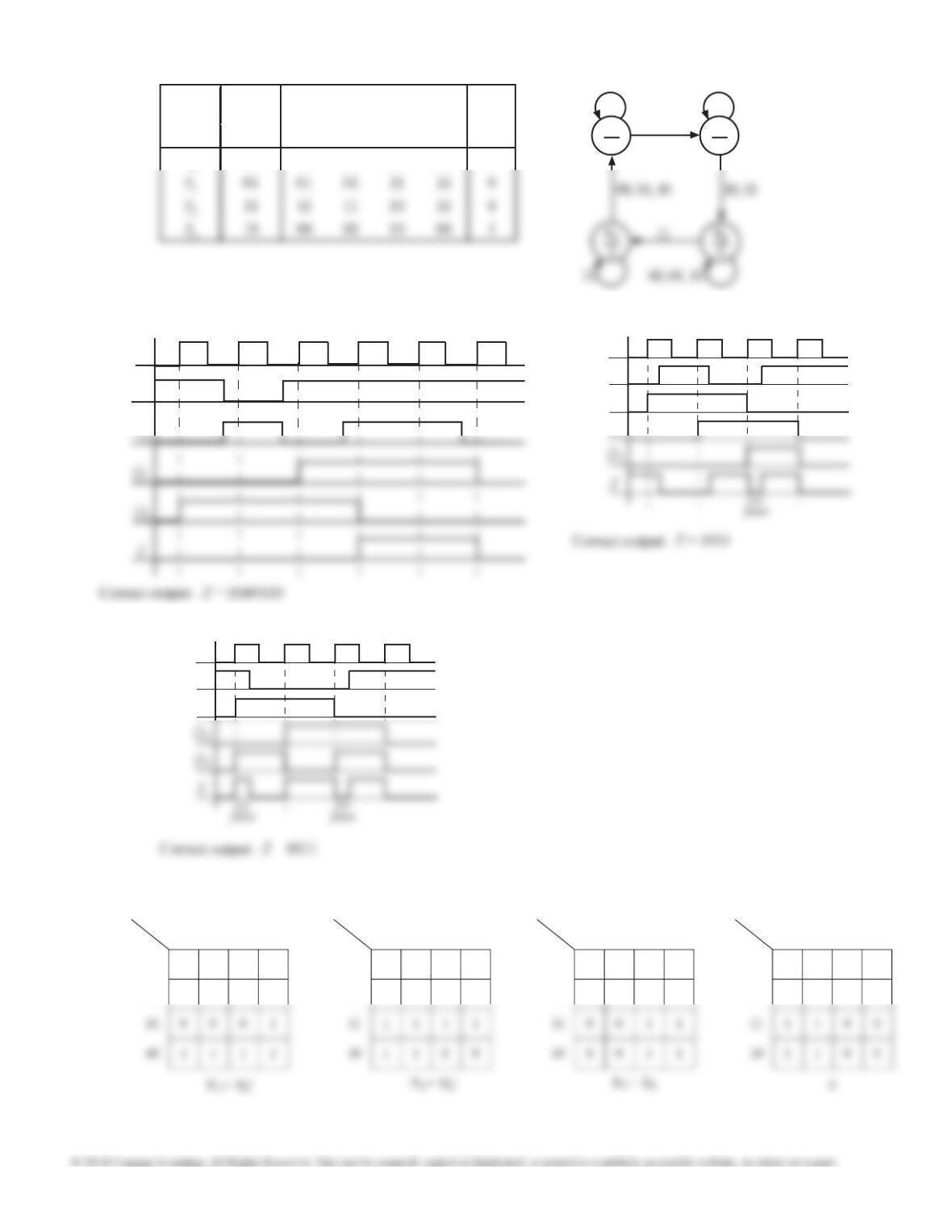

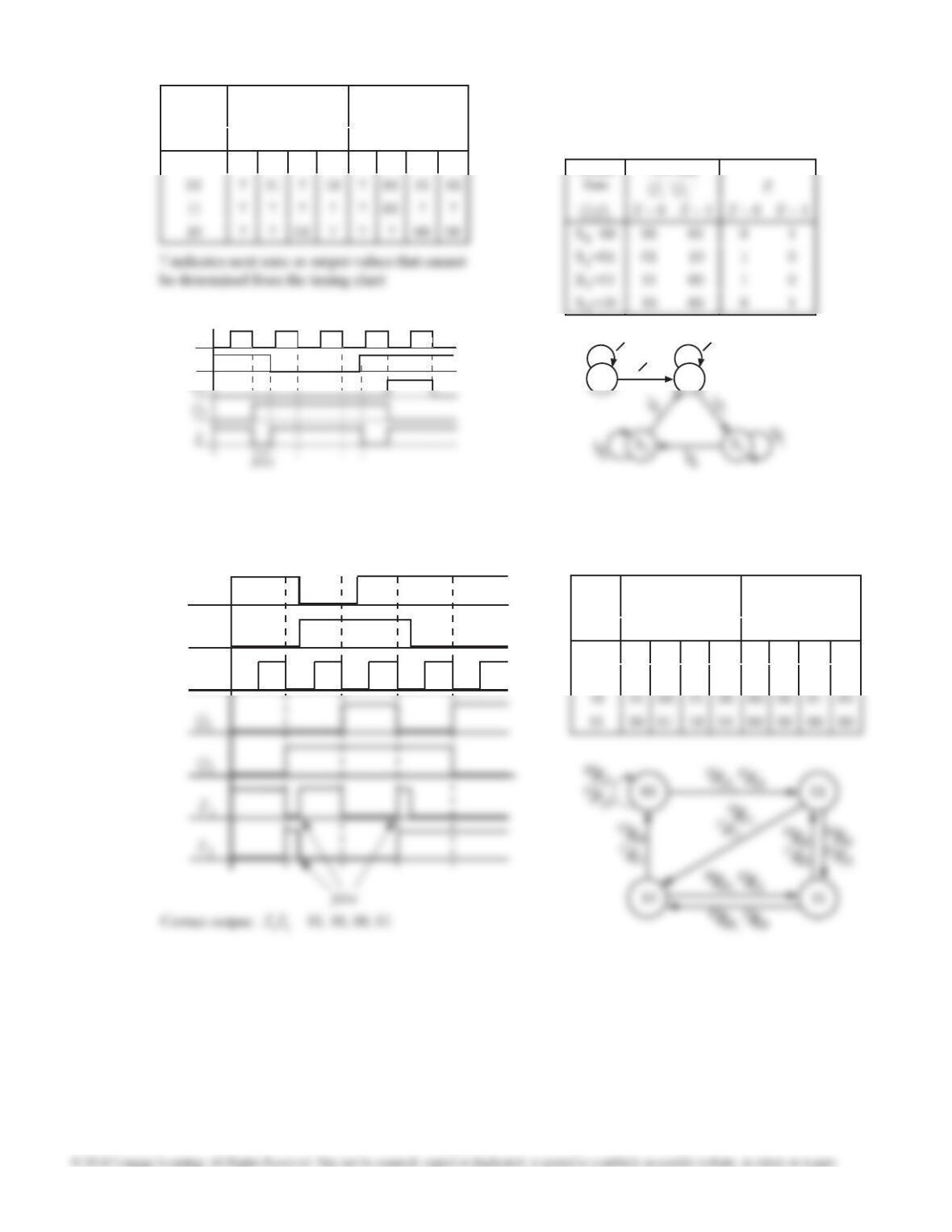

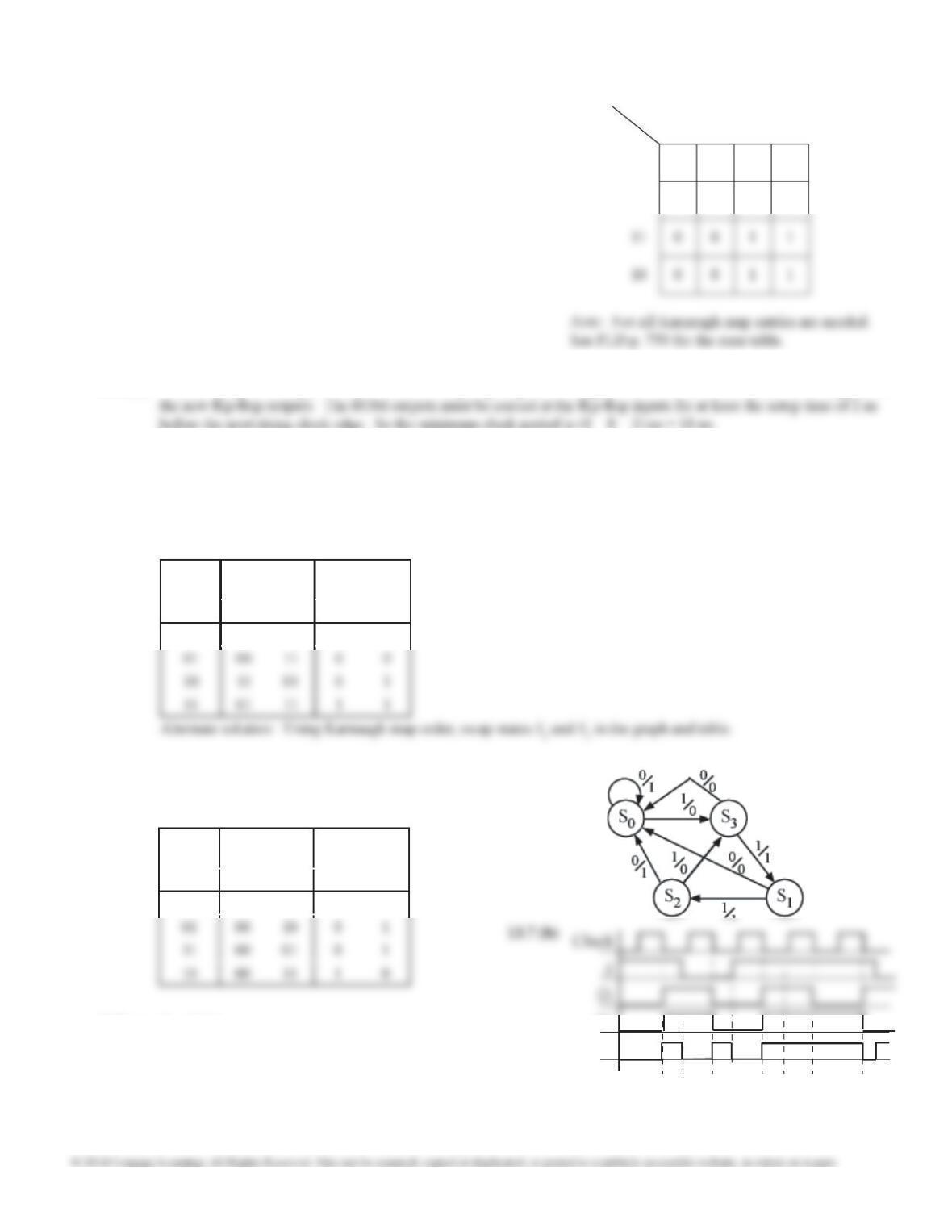

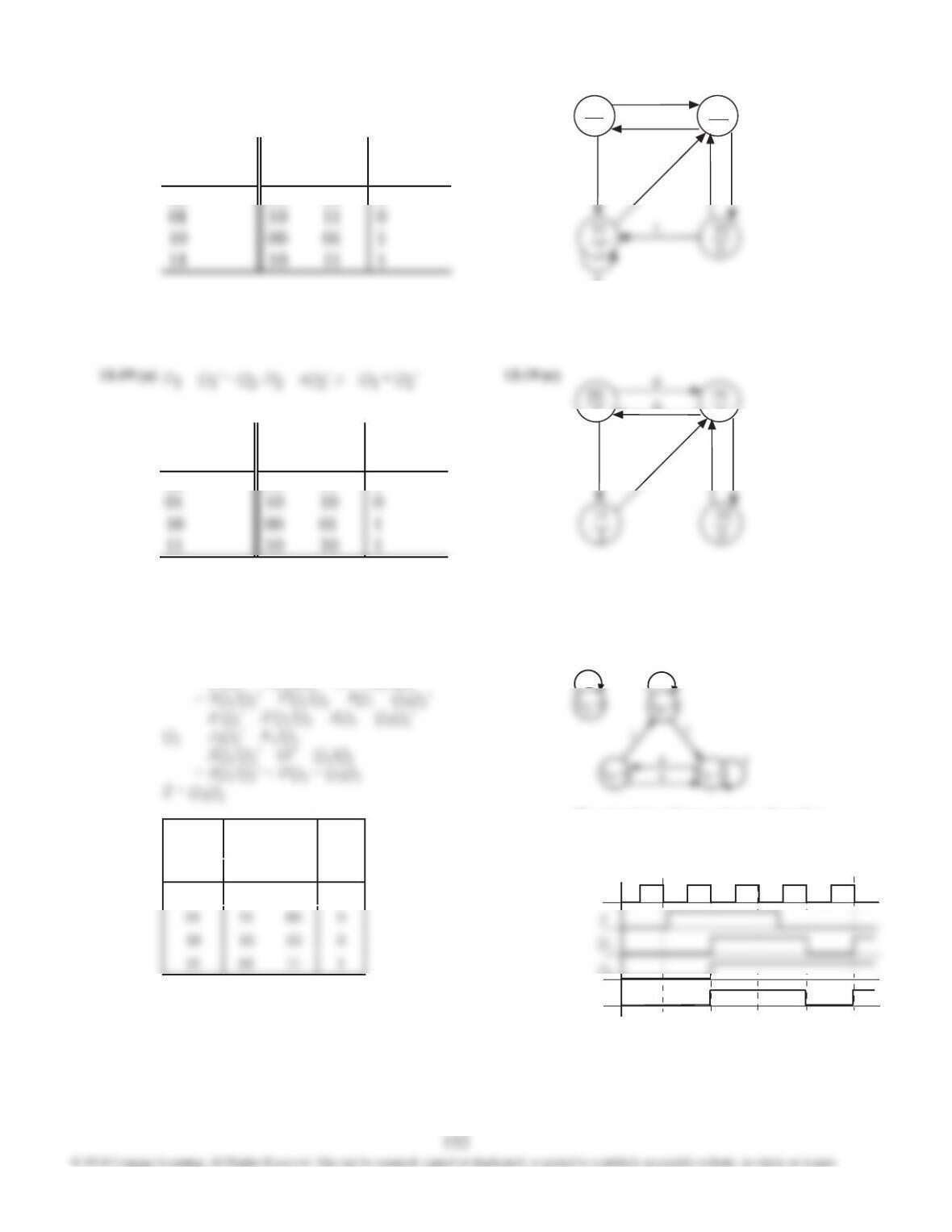

13.23 Clock Cycle Information Gathered

1Q1Q2 = 00, X1X2 = 01 ⇒ Z1Z2 = 10, Q1

+Q2

+ = 01

2Q1Q2 = 01, X1X2 = 01 ⇒ Z1Z2 = 01; X1X2 = 10 ⇒ Z1Z2 = 10, Q1

+Q2

+ = 10

Note: When Q1Q2 = 01,

the outputs Z1Z2 vary

depending on the inputs

X1X2, so this is a Mealy

Present

State

Q1

+Q2

+

X1X2=

Z1Z2

X1X2=

Q1Q200 01 11 10 00 01 11 10

00 ? 01 ? ? ? 10 ? ?