138

Unit 12 Solutions

011

100

001

000

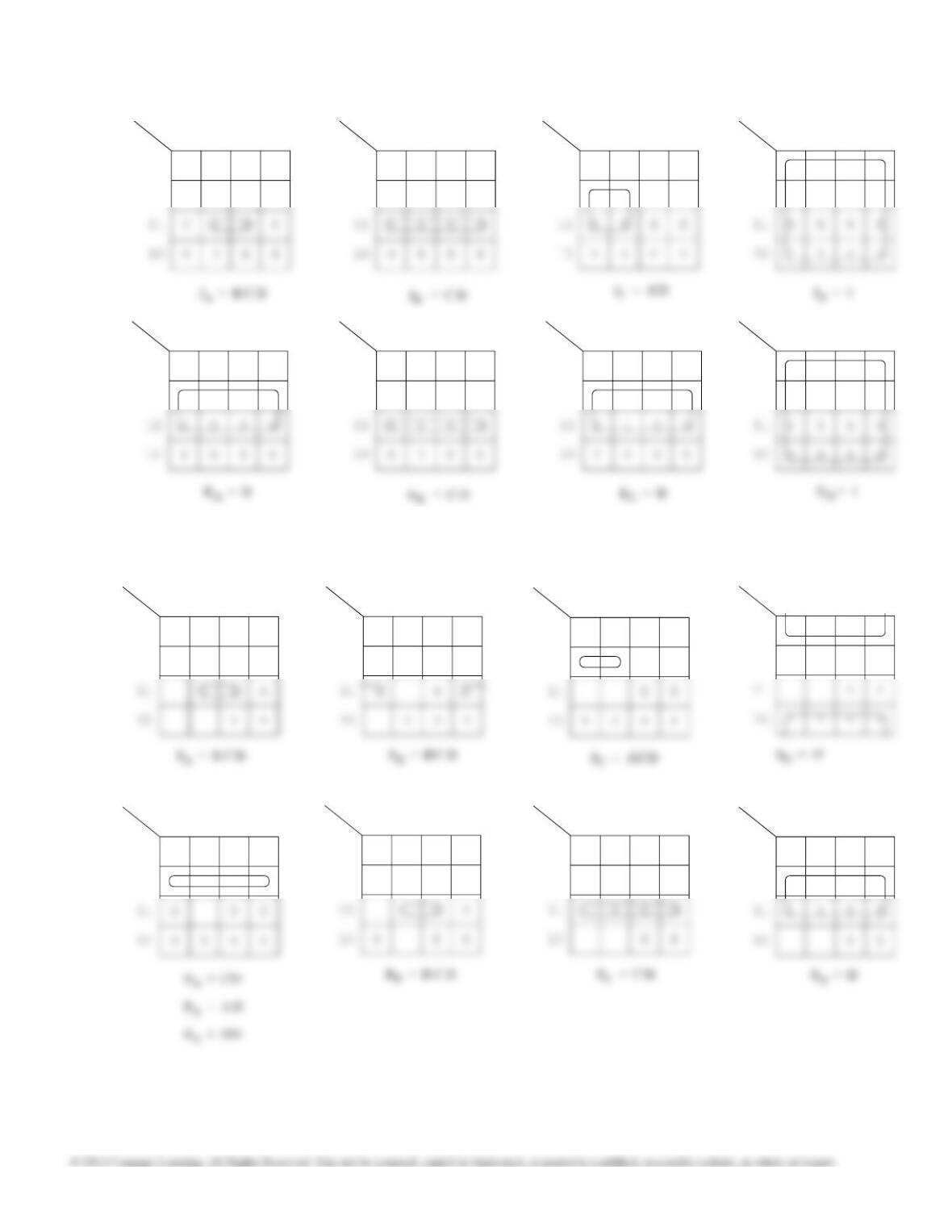

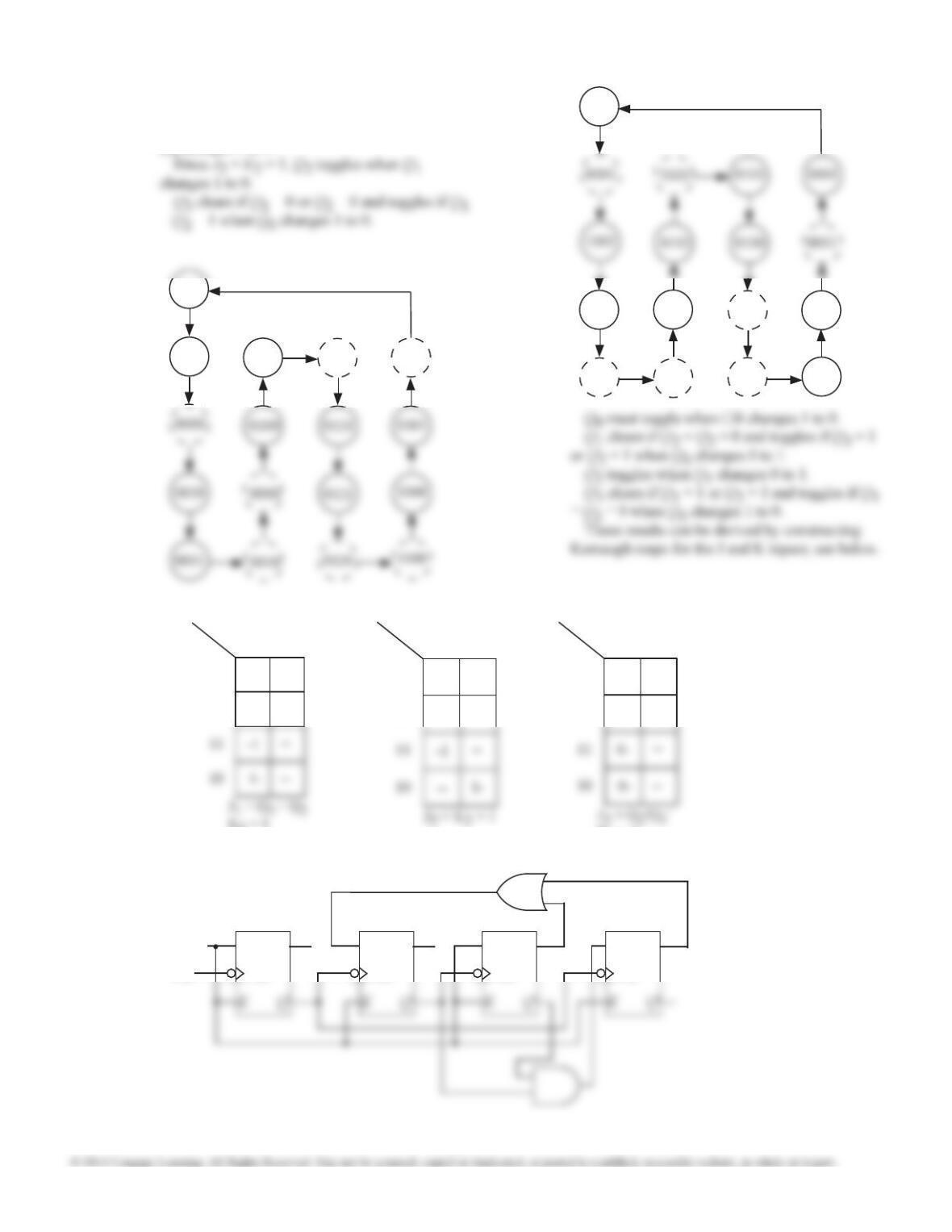

12.27 (a) (b) There are two answers:

Sin = Q2 ⊕ Q3 or

Sin = Q0 ⊕ Q3.

(c) The state 0000 can

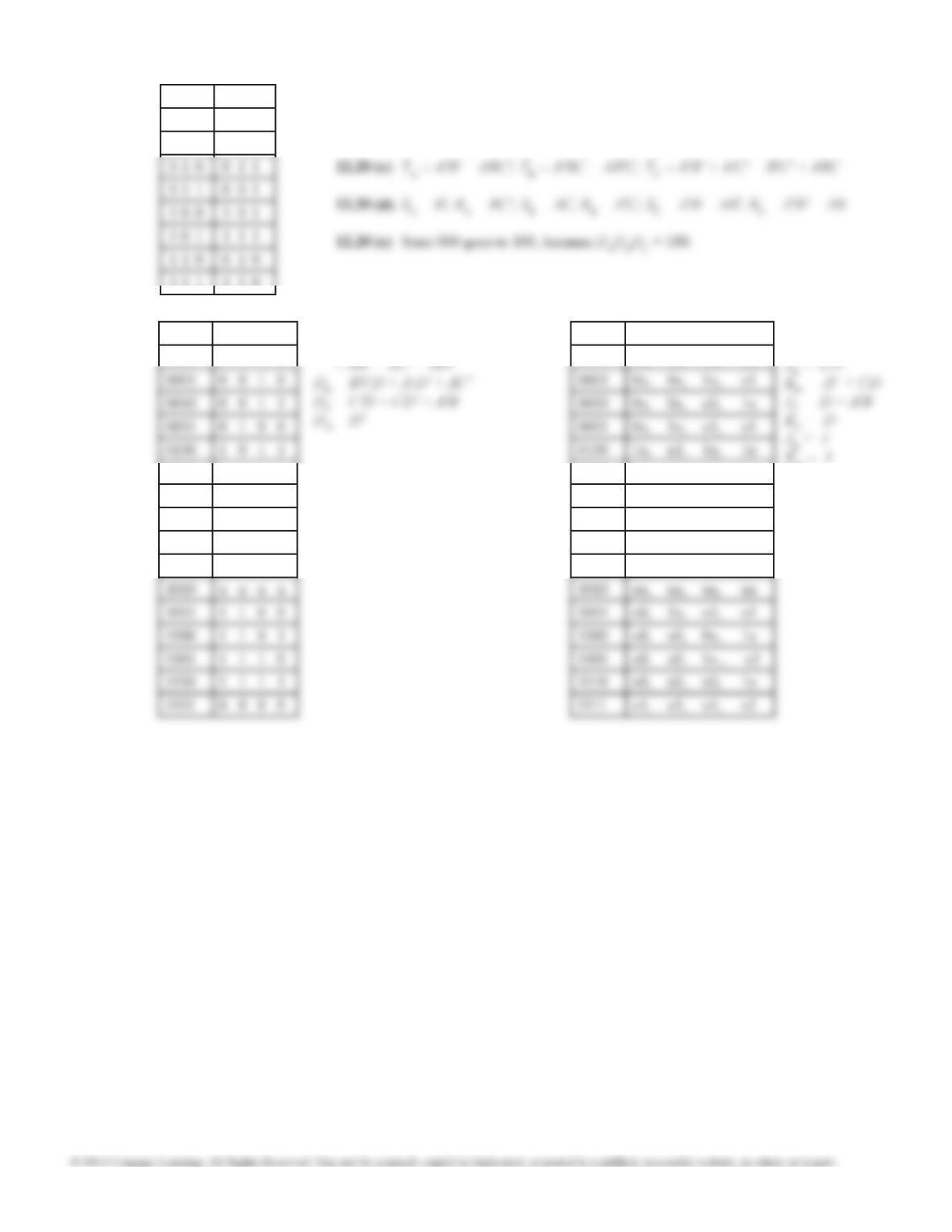

Sin Q0Q1

Q2Q300 01 11 10

00

01

1

1

1

1

0

0 00

12.27 (c)

(cont.)

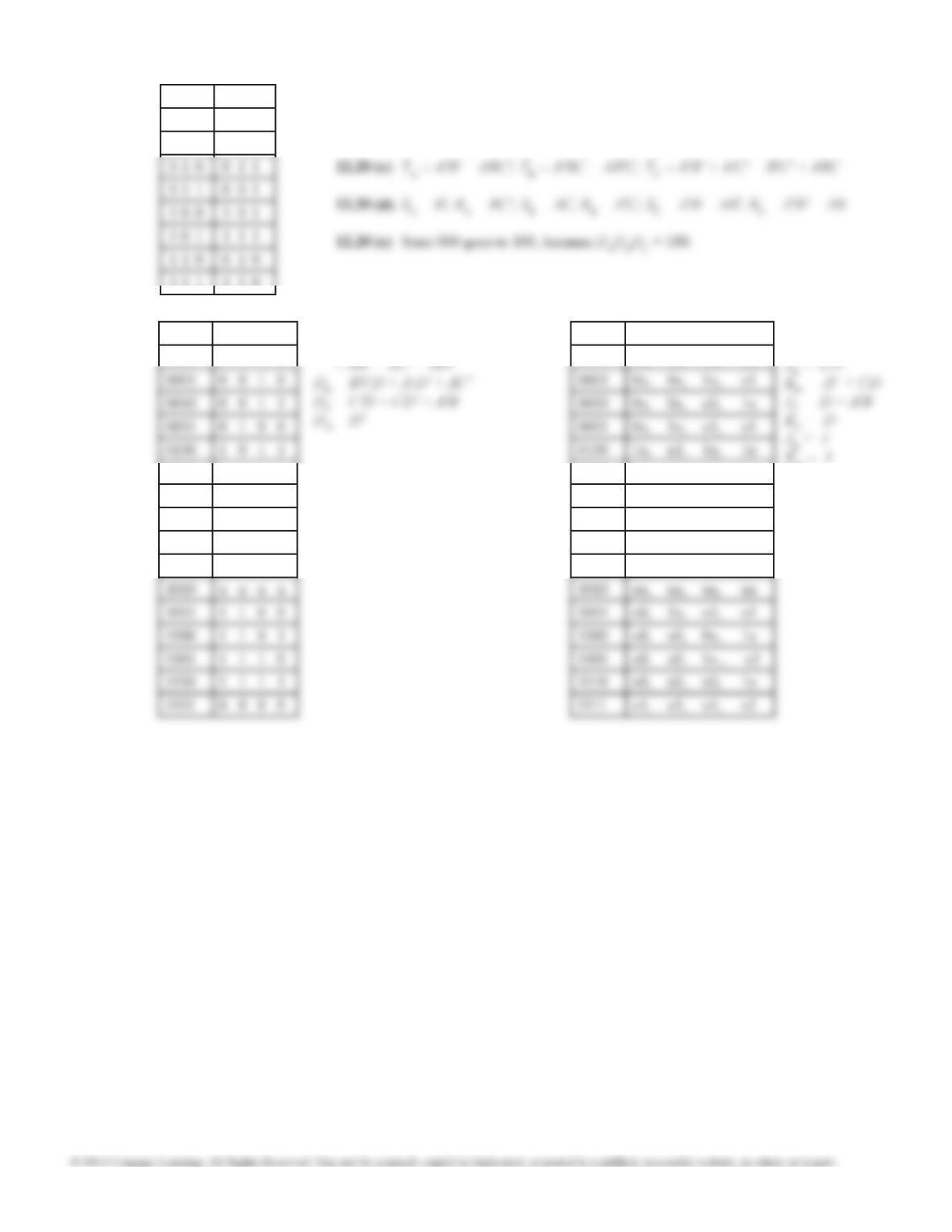

12.28 (a) 000, 100, 110, 111, 011, 001

010, 101.

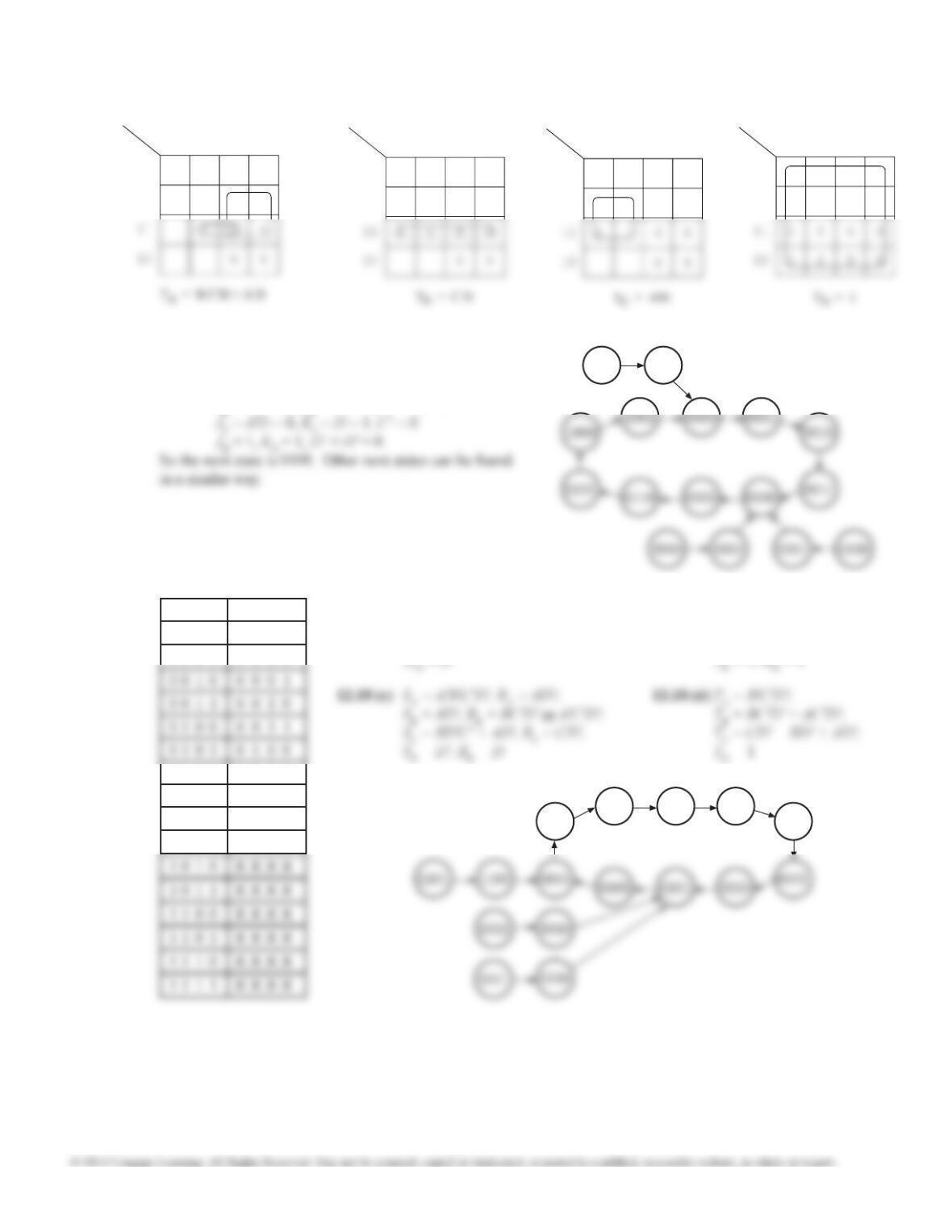

12.29 (a) Skips all 1’s: Dn = Q2′Q1′

(b)Skips all 0’s:

12.30 (a) The changed transition is (QnQn-1 ... Q2Q1) = (11 ... 10) → (01 ... 11): Jn = Q1′, Kn = Q2

(b) The changed transition is (QnQn-1 ... Q2Q1) = (00 ... 01) → (10 ... 00): Jn = Q2′, Kn = Q1

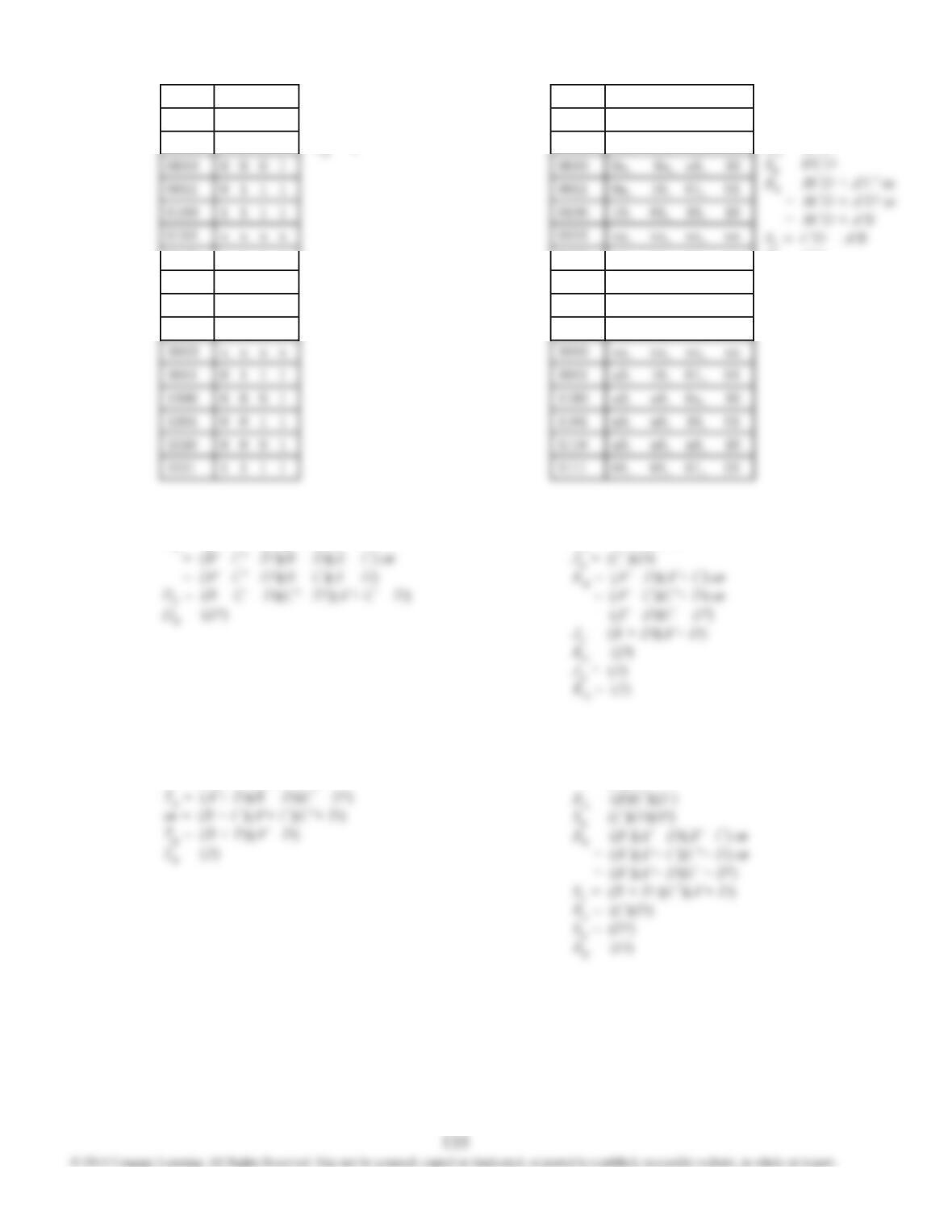

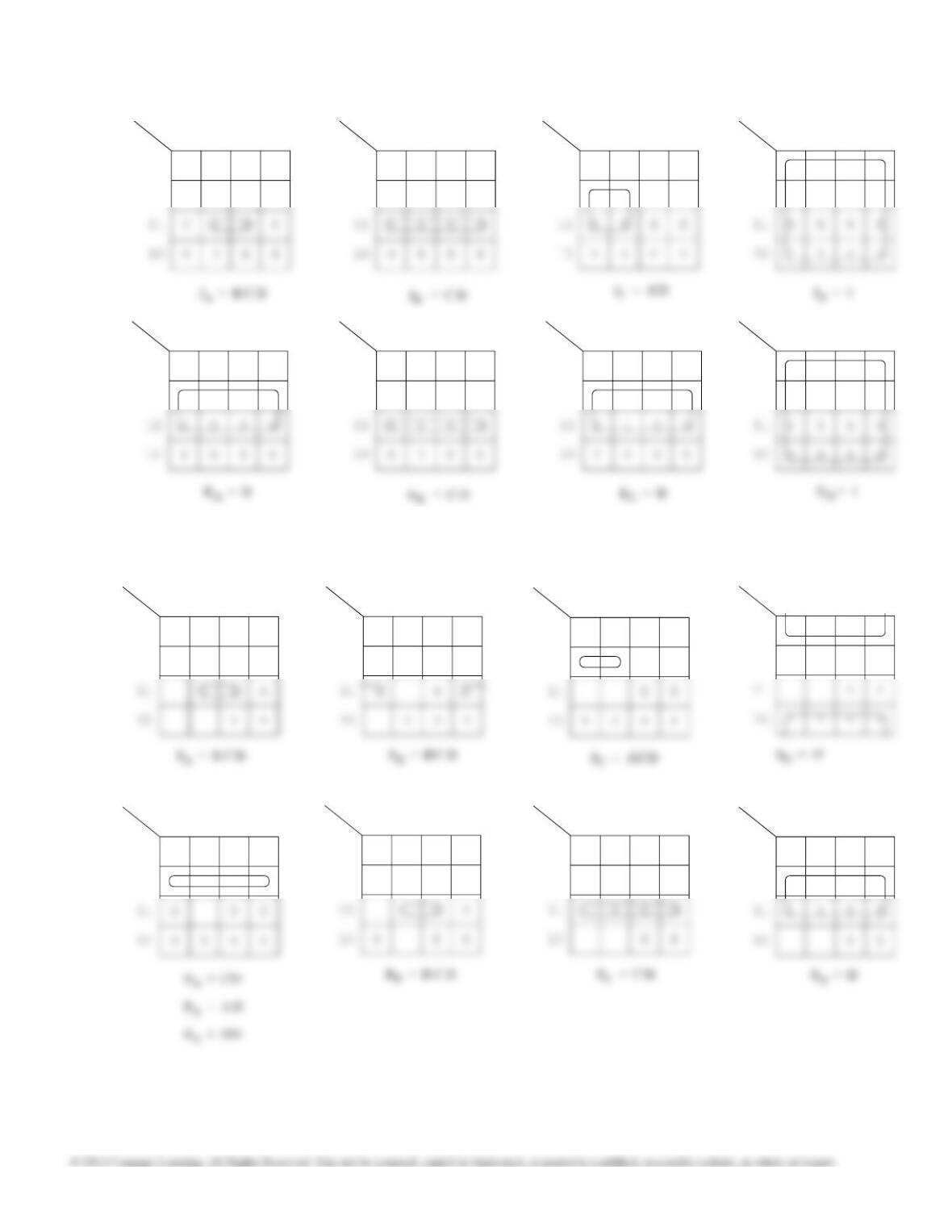

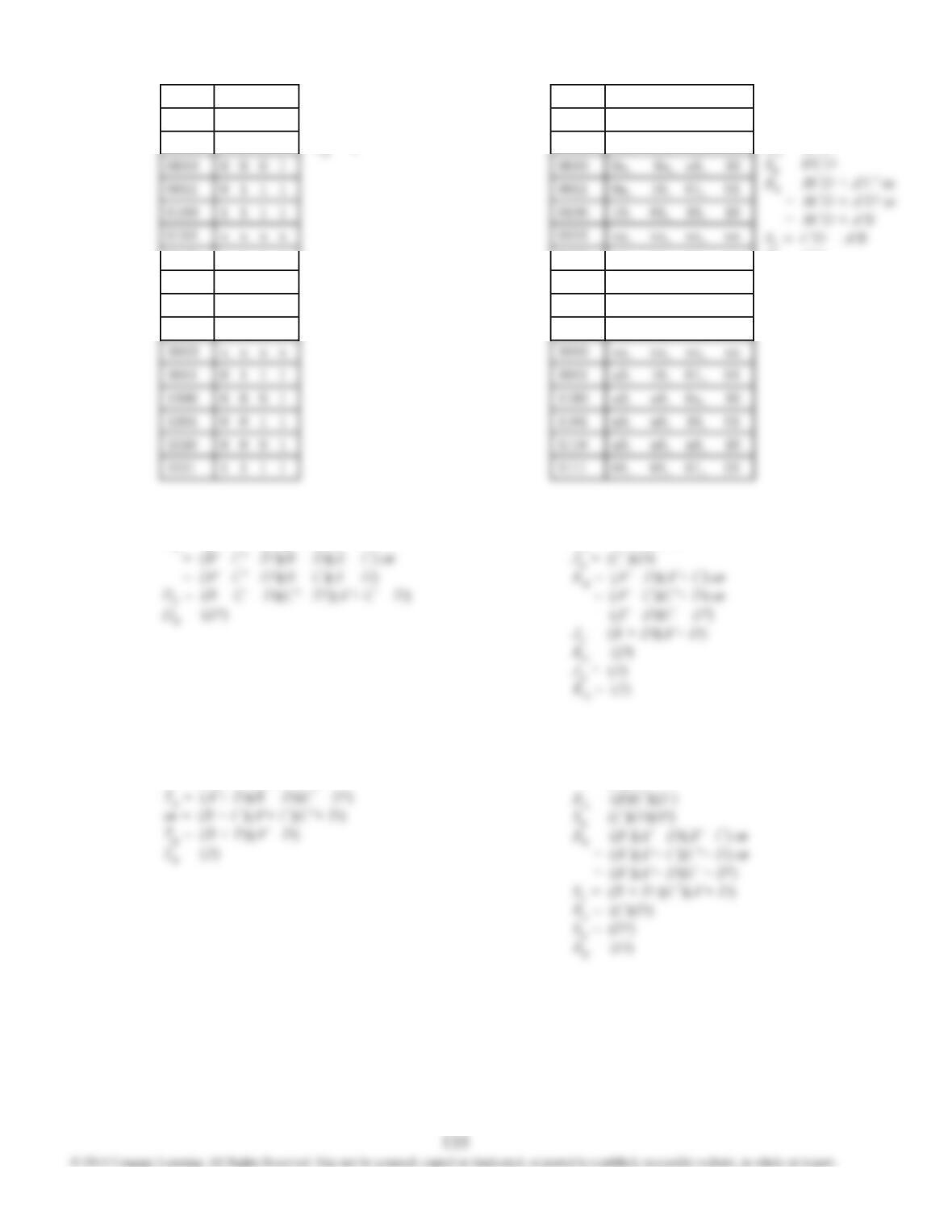

12.31 (a) All stages toggle the same as for a binary counter

except when the count becomes 1001, in which

case stages Q0, Q1 and Q2 respond the same as

for a binary counter, but Q3 must toggle (reset).

12.31 (b) All stages toggle the same as for a binary counter

for counts 0011 through 1011. For count 1100

stages 3 and 2 must reset and stage 1 must set

while stage 0 toggles as it does it does for a binary

K3 = Q0Q1Q2 + Q2Q3

K3 can be further simplified to K3 = Q2Q3.

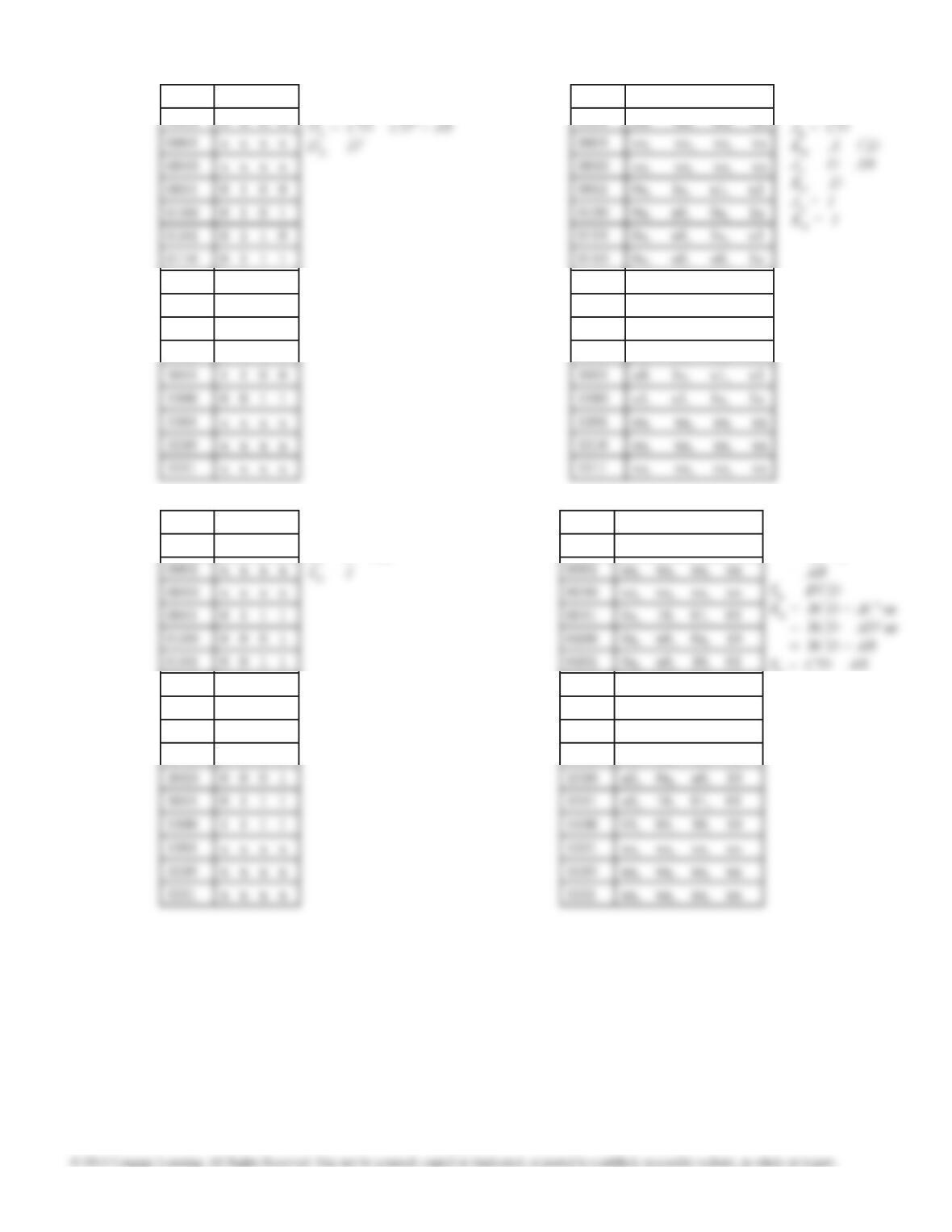

12.31 (c) To create a design that can be cascaded, we need

to add a count enable input, CE, which is ANDed

with the above equations, and terminal count