355

NAME _______________________________ PASSWORD _________ DATE __________

(signature)

READINESS TEST - UNIT 5R - FORM A*

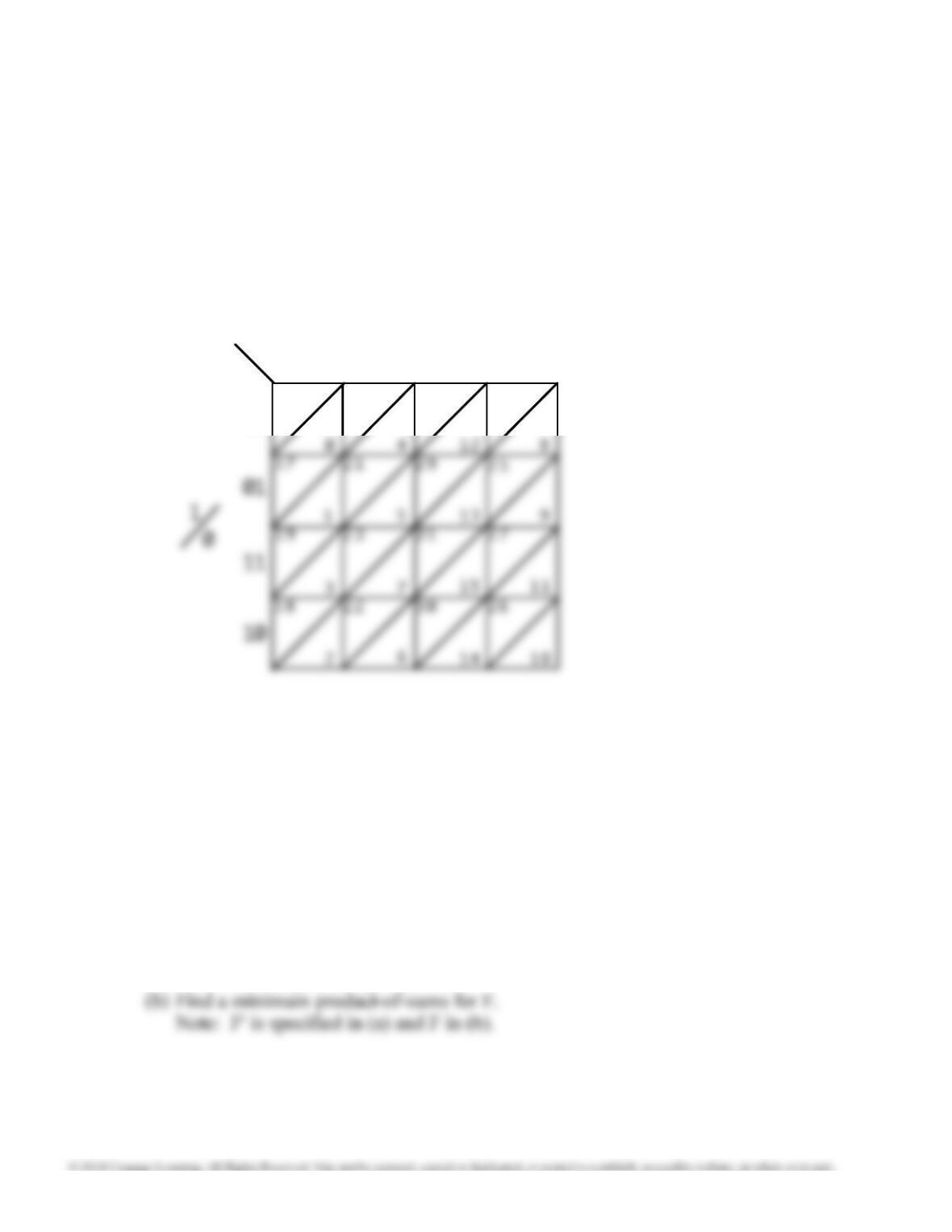

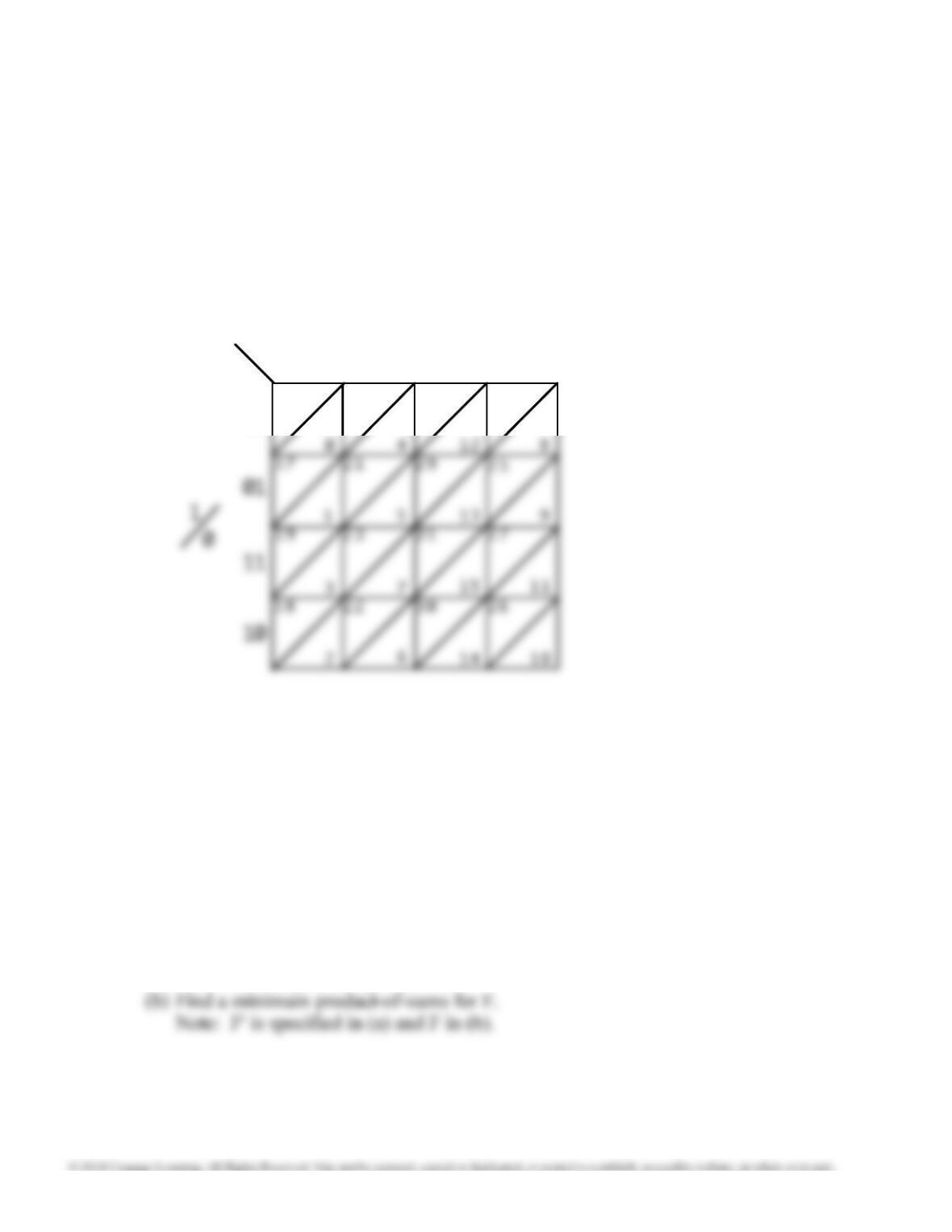

1. F(a, b, c, d, e) = Σ m(0, 1, 2, 6, 7, 8, 16, 17, 19, 20, 25, 26, 29, 31) + Σ d(3, 5, 18, 27)

(a) Find the essential prime implicants of F and indicate the minterm which makes each one

essential.

(b) Find a minimum sum-of-products expression for F.

2. F(a, b, c, d) = Σ m(7, 11, 12, 14) + Σ d(0, 10)

(a) Find all of the prime implicants of F'.